1/2ページ

ダウンロード(2.5Mb)

4K 対応の超低遅延なMPEG 規格コーデック技術

System-On-Chip Technologies Inc.(SOC 社)は、1995 年にカナダにあるウィルフリッド・ローリエ大学でコーデックの実験・研究からスタートし、2008 年に現在の会社を設立しました。FPGA に特化した映像コーデックのコア技術と製品の開発とそのサービス、販売に至るまで幅広いビジネスを展開しています。

SOC 社は、自社開発し利用実績のある次世代映像技術4K/8K のエンコード・デコードIP コア技術を容易に利用できる製品として、FPGA を利用したボードソリューションを開発しました。

このカタログについて

| ドキュメント名 | 4K H.264/H.265ビデオコーデック ボードソリューション |

|---|---|

| ドキュメント種別 | 製品カタログ |

| ファイルサイズ | 2.5Mb |

| 取り扱い企業 | 富士ソフト株式会社 (この企業の取り扱いカタログ一覧) |

この企業の関連カタログ

このカタログの内容

Page1

System-On-Chip Technologies社製

4K H.264/H.265ビデオコーデック

ボードソリューション

4K 対応の超低遅延な MPEG 規格コーデック技術

System-On-Chip Technologies Inc(. SOC 社)は、1995 年にカナダにあるウィルフリッド・ローリエ大学

でコーデックの実験・研究からスタートし、2008 年に現在の会社を設立しました。FPGA に特化した映像コ

ーデックのコア技術と製品の開発とそのサービス、販売に至るまで幅広いビジネスを展開しています。

SOC 社は、自社開発し利用実績のある次世代映像技術 4K/8K のエンコード・デコード IP コア技術を容易に

利用できる製品として、FPGA を利用したボードソリューションを開発しました。

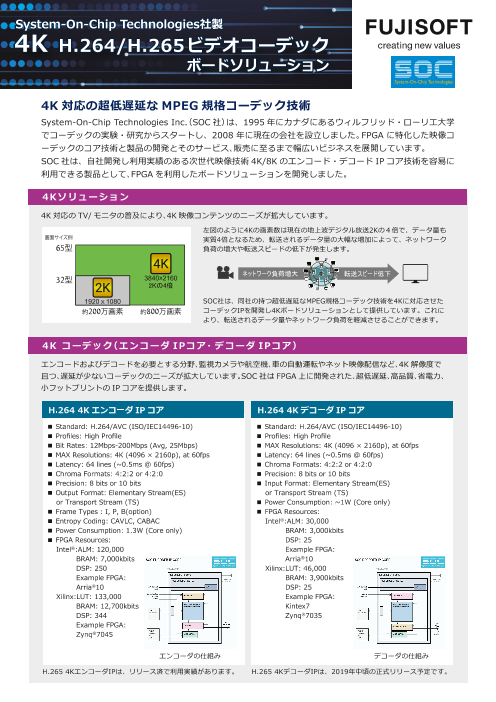

4Kソリューション

4K 対応の TV/ モニタの普及により、4K 映像コンテンツのニーズが拡大しています。

左図のように4Kの画素数は現在の地上波デジタル放送2Kの4倍で、データ量も

画面サイズ例 実質4倍となるため、転送されるデータ量の大幅な増加によって、ネットワーク

65型 負荷の増大や転送スピードの低下が発生します。

32型 3840x2160

2Kの4倍

1920x1080 SOC社は、同社の持つ超低遅延なMPEG規格コーデック技術を4Kに対応させた

約200万画素 約800万画素 コーデックIPを開発し4Kボードソリューションとして提供しています。これに

より、転送されるデータ量やネットワーク負荷を軽減させることができます。

4K コーデック(エンコーダ IPコア・デコーダ IPコア)

エンコードおよびデコードを必要とする分野、監視カメラや航空機、車の自動運転やネット映像配信など、4K 解像度で

且つ、遅延が少ないコーデックのニーズが拡大しています。SOC 社は FPGA 上に開発された、超低遅延、高品質、省電力、

小フットプリントの IP コアを提供します。

■ Standard: H.264/AVC (ISO/IEC14496-10) ■ Standard: H.264/AVC (ISO/IEC14496-10)

■ Profiles: High Profile ■ Profiles: High Profile

■ Bit Rates: 12Mbps-200Mbps (Avg, 25Mbps) ■ MAX Resolutions: 4K (4096 × 2160p), at 60fps

■ MAX Resolutions: 4K (4096 × 2160p), at 60fps ■ Latency: 64 lines (~0.5ms @ 60fps)

■ Latency: 64 lines (~0.5ms @ 60fps) ■ Chroma Formats: 4:2:2 or 4:2:0

■ Chroma Formats: 4:2:2 or 4:2:0 ■ Precision: 8 bits or 10 bits

■ Precision: 8 bits or 10 bits ■ Input Format: Elementary Stream(ES)

■ Output Format: Elementary Stream(ES) or Transport Stream (TS)

or Transport Stream (TS) ■ Power Consumption: ~1W (Core only)

■ Frame Types : I, P, B(option) ■ FPGA Resources:

■ Entropy Coding: CAVLC, CABAC Intel®:ALM: 30,000

■ Power Consumption: 1.3W (Core only) BRAM: 3,000kbits

■ FPGA Resources: DSP: 25

Intel®:ALM: 120,000 Example FPGA:

BRAM: 7,000kbits Arria®10

DSP: 250 Xilinx:LUT: 46,000

Example FPGA: BRAM: 3,900kbits

Arria®10 DSP: 25

Xilinx:LUT: 133,000 Example FPGA:

BRAM: 12,700kbits Kintex7

DSP: 344 Zynq®7035

Example FPGA:

Zynq®7045

エンコーダの仕組み デコーダの仕組み

H.265 4KエンコーダIPは、リリース済で利用実績があります。 H.265 4KデコーダIPは、2019年中頃の正式リリース予定です。

Page2

4Kボードソリューション

4Kボードソリューションは、4K解像度のコーデックが実装されたモジュール、メモリ、I/Oなどを搭載したもので、

開発をすること無く4Kエンコード・デコードを実現します。エンコーダ・デコーダ技術は、FPGA上のIPコアのため

アップデートが可能で、最新のMPEG規格(H.264 AVCからH.265 HEVCなど)へ移行も可能です。

外形寸法 外形寸法

ボード仕様 ボード仕様

デモンストレーション実例

2枚の4Kボードソリューションを使用して①4Kカメラや放送装置の入力から H.264 4K/60fps のエンコード。続けて

②MPEG-TSフォーマットを Ethernet 経由で転送しH.264 4K/60fps のデコード。そして③4Kモニタへ出力するまで

を超低遅延かつ高品質で実施。

①入力

or

③出力

②転送

この数値はエンコード処理とデコード処理の値です。

入力・転送・出力にかかる時間は含んでいません。

※本印刷物に記載の内容および製品・サービスの仕様は、予告なく変更する場合があります。

※記載されている社名および製品名は、各社の商標または登録商標です。

©2017 FUJISOFT INCORPORATED. All rights reserved.

www.fsi.co.jp 0120-593-111 受付時間9:00 ~ 17:00(土・日・祝除く)

富士ソフト 組み込み製品 2018 Nov / rev1.1

お問合せ窓口:et-solution@fsi.co.jp

組み込み WEB サイト:www.fsi-embedded.jp

富士ソフト SOC 検索