1/2ページ

ダウンロード(1.3Mb)

高速デジタルデザインや無線通信でデータレートを上げるには、相加性位相雑音が低く、ジッタ減衰量の大きいSerDes PLLおよびクロックシンセサイザーが必要です。最新のデザインは、通常、2ステージアーキテクチャーに従い、ジッタ・アッテネータ・ステージと周波数シンセサイザーステージで構成されています。位相雑音感度が高いため、これらのテストには位相雑音アナライザが測定器として最適です。PLLへの信号印加には、超低位相雑音の追加信号源が必要となります。

このカタログについて

| ドキュメント名 | 高速デジタルデザインのPLLの相加性位相雑音と ジッタ減衰量の確認 |

|---|---|

| ドキュメント種別 | 製品カタログ |

| ファイルサイズ | 1.3Mb |

| 取り扱い企業 | ローデ・シュワルツ・ジャパン株式会社 (この企業の取り扱いカタログ一覧) |

この企業の関連カタログ

このカタログの内容

Page1

高速デジタルデザインのPLLの相加性位相雑音と

ジッタ減衰量の確認

高速デジタルデザインや無線通信でデータレートを上げるには、相加性位相雑音が低く、ジッ

タ減衰量の大きいSerDes PLLおよびクロックシンセサイザーが必要です。最新のデザインは、通

常、2ステージアーキテクチャーに従い、ジッタ・アッテネータ・ステージと周波数シンセサイザー

ステージで構成されています。位相雑音感度が高いため、これらのテストには位相雑音アナラ

イザが測定器として最適です。PLLへの信号印加には、超低位相雑音の追加信号源が必要とな

ります。

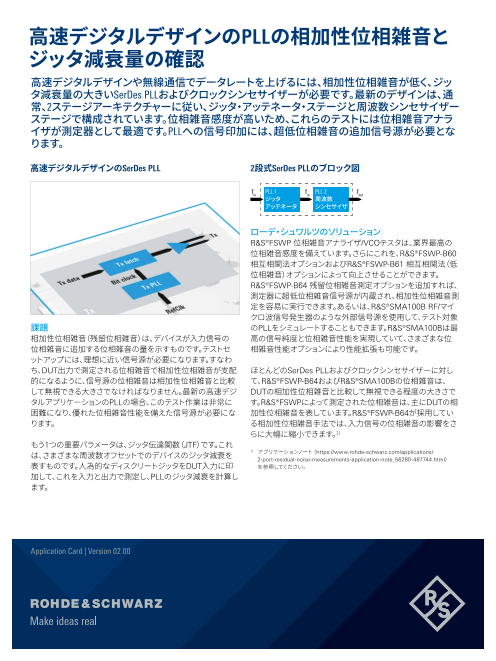

高速デジタルデザインのSerDes PLL 2段式SerDes PLLのブロック図

f PLL 1 f PLL 2

in in fout

ジッタ 周波数

アッテネータ シンセサイザ

ローデ・シュワルツのソリューション

R&S®FSWP 位相雑音アナライザ/VCOテスタは、業界最高の

位相雑音感度を備えています。さらにこれを、R&S®FSWP-B60

相互相関法オプションおよびR&S®FSWP-B61 相互相関法(低

位相雑音)オプションによって向上させることができます。

R&S®FSWP-B64 残留位相雑音測定オプションを追加すれば、

測定器に超低位相雑音信号源が内蔵され、相加性位相雑音測

定を容易に実行できます。あるいは、R&S®SMA100B RF/マイ

クロ波信号発生器のような外部信号源を使用して、テスト対象

課題 のPLLをシミュレートすることもできます。R&S®SMA100Bは最

相加性位相雑音(残留位相雑音)は、デバイスが入力信号の 高の信号純度と位相雑音性能を実現していて、さまざまな位

位相雑音に追加する位相雑音の量を示すものです。テストセ 相雑音性能オプションにより性能拡張も可能です。

ットアップには、理想に近い信号源が必要になります。すなわ

ち、DUT出力で測定される位相雑音で相加性位相雑音が支配 ほとんどのSerDes PLLおよびクロックシンセサイザーに対し

的になるように、信号源の位相雑音は相加性位相雑音と比較 て、R&S®FSWP-B64およびR&S®SMA100Bの位相雑音は、

して無視できる大きさでなければなりません。最新の高速デジ DUTの相加性位相雑音と比較して無視できる程度の大きさで

タルアプリケーションのPLLの場合、このテスト作業は非常に す。R&S®FSWPによって測定された位相雑音は、主にDUTの相

困難になり、優れた位相雑音性能を備えた信号源が必要にな 加性位相雑音を表しています。R&S®FSWP-B64が採用してい

ります。 る相加性位相雑音手法では、入力信号の位相雑音の影響をさ

らに大幅に縮小できます。1)

もう1つの重要パラメータは、ジッタ伝達関数(JTF)です。これ

1)

は、さまざまな周波数オフセットでのデバイスのジッタ減衰を アプリケーションノート(https://www.rohde-schwarz.com/applications/

2-port-residual-noise-measurements-application-note_56280-487744.html)

表すものです。人為的なディスクリートジッタをDUT入力に印 を参照してください。

加して、これを入力と出力で測定し、PLLのジッタ減衰を計算し

ます。

Application Card | Version 02.00

Page2

他社製のソリューションとは異なり、手動で外部移相器との直

交性を実現する必要はありません。R&S®FSWPは自動的にこ

れを行い、使いやすい相加性位相雑音測定の新しい基準を打

ち立てています。

R&S®SMA100Bは、PLLのジッタ伝達関数の測定にも使用で

きます。PM変調(R&S®SMAB-K720 オプション)を介して、人為

的なジッタが信号源に追加されます。R&S®FSWPはDUT出力

で実際のジッタを測定して、DUT入力でのジッタに対してそれ

をノーマライズし、ジッタ減衰を特定します。このアプリケーショ

ンカードのダウンロードセクションに外部ツールがあります。 セットアップ例:

R&S®SMA100B(R&S®SMAB-K720オプションが必要)とは別 ► R&S®FSWPによる相加性位相雑音測定

に、R&S®FSWP(R&S®FSWP-B60またはR&S®FSWP-B61オプ ► R&S®FSWPとR&S®SMA100BによるJTF測定

ションが必要)とR&S®FSPNをサポートします。このツールは、

さまざまな周波数オフセットでジッタ減衰を測定し、ピークや3

dB帯域幅を含む、DUTのジッタ伝達関数を提供します(以下の ジッタ伝達関数測定セットアップ

スクリーンショットを参照)。

基準

まとめ クロック f PLL 1 f PLL 2

in in fout ビットロック

jitter ジッタ 周波数 jitter

R&S®FSWPは、高速デジタルデザインでPLLの相加性 in アッテネータ シンセサイザ out

位相雑音をテストするのに必要な機能を備えていま

す。R&S®SMA100Bを超低位相雑音信号源として外部で使用 DUT

すれば、PLLのジッタ伝達関数(JTF)を測定できます。 Jitter

JTF=20log out

Jitterin

詳細はこちら

www.rohde-schwarz.com/product/fswp

www.rohde-schwarz.com/product/fspn

www.rohde-schwarz.com/product/sma100b

ジッタ伝達関数の自動測定

Rohde & Schwarz GmbH & Co. KG R&S® は、ドイツRohde & Schwarz の商標または登録商標です。

www.rohde-schwarz.com PD 5216.0573.96 | Version 02.00 | 6月 2022 (sk)

高速デジタルデザインのPLLの相加性位相雑音とジッタ減衰量の確認

ローデ・シュワルツ トレーニング 掲載されている記事・図表などの無断転載を禁止します。

www.training.rohde-schwarz.com おことわりなしに掲載内容の一部を変更させていただくことがあります。

ローデ・シュワルツ カスタマーサポート あらかじめご了承ください。

www.rohde-schwarz.com/support © 2018 - 2022 Rohde & Schwarz GmbH & Co. KG | 81671 Munich, Germany

5216.0573.96 02.00 PDP/PDW 1 ja 5216057396