1/59ページ

ダウンロード(961.2Kb)

Programmable Gain Instrumentation Amplifier

このカタログについて

| ドキュメント名 | ADA4254 Zero Drift, High Voltage, Low Power |

|---|---|

| ドキュメント種別 | 製品カタログ |

| ファイルサイズ | 961.2Kb |

| 取り扱い企業 | マウザー・エレクトロニクス (この企業の取り扱いカタログ一覧) |

この企業の関連カタログ

このカタログの内容

Page1

FEATURES、APPLICATIONS、GENERAL DESCRIPTION、SIMPLIFIED FUNCTIONAL BLOCK DIAGRAM、COMPANION PRODUCTS

Zero Drift, High Voltage, Low Power,

Programmable Gain Instrumentation Amplifier

Data Sheet ADA4254

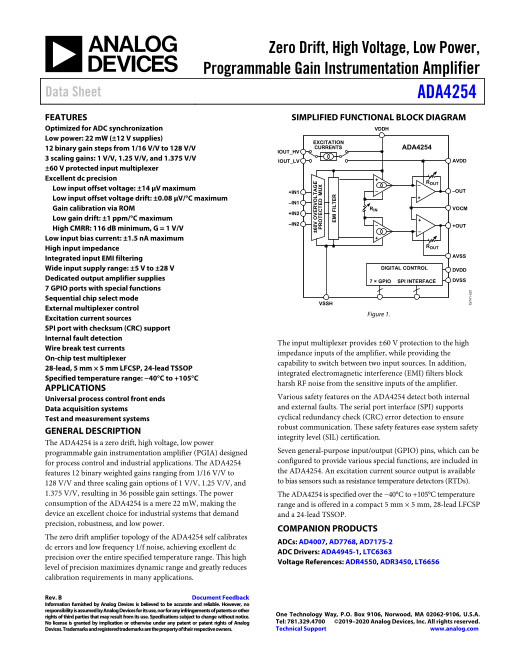

FEATURES SIMPLIFIED FUNCTIONAL BLOCK DIAGRAM

Optimized for ADC synchronization VDDH

Low power: 22 mW (±12 V supplies)

EXCITATION

12 binary gain steps from 1/16 V/V to 128 V/V CURRENTS ADA4254

IOUT_HV

3 scaling gains: 1 V/V, 1.25 V/V, and 1.375 V/V IOUT_LV AVDD

±60 V protected input multiplexer

Excellent dc precision + ROUT

Low input offset voltage: ±14 μV maximum –

+IN1 – –OUT

Low input offset voltage drift: ±0.08 μV/°C maximum +

–IN1

Gain calibration via ROM RIN VOCM

+IN2

Low gain drift: ±1 ppm/°C maximum +

–IN2

High CMRR: 116 dB minimum, G = 1 V/V – +OUT

–

Low input bias current: ±1.5 nA maximum +

High input impedance ROUT

Integrated input EMI filtering AVSS

Wide input supply range: ±5 V to ±28 V DIGITAL CONTROL DVDD

Dedicated output amplifier supplies 7 × GPIO SPI INTERFACE DVSS

7 GPIO ports with special functions

Sequential chip select mode

VSSH

External multiplexer control

Figure 1.

Excitation current sources

SPI port with checksum (CRC) support

Internal fault detection The input multiplexer provides ±60 V protection to the high

Wire break test currents impedance inputs of the amplifier, while providing the

On-chip test multiplexer capability to switch between two input sources. In addition,

28-lead, 5 mm × 5 mm LFCSP, 24-lead TSSOP

integrated electromagnetic interference (EMI) filters block

Specified temperature range: −40°C to +105°C

APPLICATIONS harsh RF noise from the sensitive inputs of the amplifier.

Universal process control front ends Various safety features on the ADA4254 detect both internal

Data acquisition systems and external faults. The serial port interface (SPI) supports

Test and measurement systems cyclical redundancy check (CRC) error detection to ensure

GENERAL DESCRIPTION robust communication. These safety features ease system safety

integrity level (SIL) certification.

The ADA4254 is a zero drift, high voltage, low power

programmable gain instrumentation amplifier (PGIA) designed Seven general-purpose input/output (GPIO) pins, which can be

for process control and industrial applications. The ADA4254 configured to provide various special functions, are included in

features 12 binary weighted gains ranging from 1/16 V/V to the ADA4254. An excitation current source output is available

128 V/V and three scaling gain options of 1 V/V, 1.25 V/V, and to bias sensors such as resistance temperature detectors (RTDs).

1.375 V/V, resulting in 36 possible gain settings. The power The ADA4254 is specified over the −40°C to +105°C temperature

consumption of the ADA4254 is a mere 22 mW, making the range and is offered in a compact 5 mm × 5 mm, 28-lead LFCSP

device an excellent choice for industrial systems that demand and a 24-lead TSSOP.

precision, robustness, and low power.

COMPANION PRODUCTS

The zero drift amplifier topology of the ADA4254 self calibrates

ADCs: AD4007, AD7768, AD7175-2

dc errors and low frequency 1/f noise, achieving excellent dc

ADC Drivers: ADA4945-1, LTC6363

precision over the entire specified temperature range. This high

Voltage References: ADR4550, ADR3450, LT6656

level of precision maximizes dynamic range and greatly reduces

calibration requirements in many applications.

Rev. B Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no

responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other

rights of third parties that may result from its use. Specifications subject to change without notice. One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

No license is granted by implication or otherwise under any patent or patent rights of Analog Tel: 781.329.4700 ©2019–2020 Analog Devices, Inc. All rights reserved.

Devices. Trademarks and registered trademarks are the property of their respective owners. Technical Support www.analog.com

±60V OVERVOLTAGE

PROTECTED MUX

EMI FILTER

15741-001

Page2

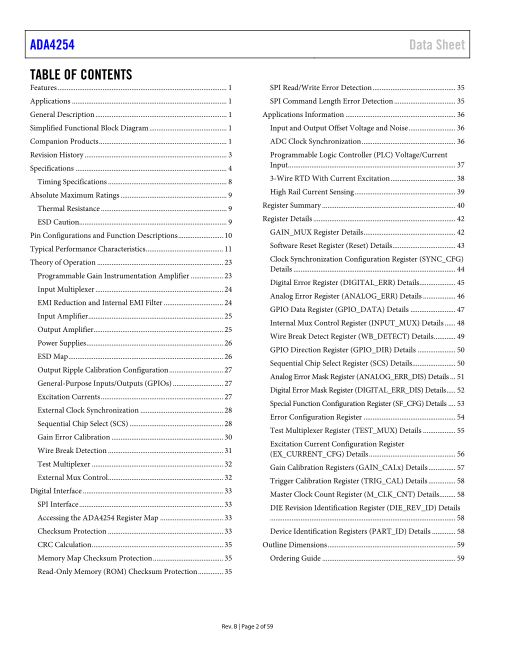

TABLE OF CONTENTS

ADA4254 Data Sheet

TABLE OF CONTENTS

Features .............................................................................................. 1 SPI Read/Write Error Detection .............................................. 35

Applications ...................................................................................... 1 SPI Command Length Error Detection .................................. 35

General Description ......................................................................... 1 Applications Information ............................................................. 36

Simplified Functional Block Diagram ........................................... 1 Input and Output Offset Voltage and Noise .......................... 36

Companion Products ....................................................................... 1 ADC Clock Synchronization .................................................... 36

Revision History ............................................................................... 3 Programmable Logic Controller (PLC) Voltage/Current

Specifications .................................................................................... 4 Input ............................................................................................. 37

Timing Specifications .................................................................. 8 3-Wire RTD With Current Excitation .................................... 38

Absolute Maximum Ratings ........................................................... 9 High Rail Current Sensing ........................................................ 39

Thermal Resistance ...................................................................... 9 Register Summary .......................................................................... 40

ESD Caution.................................................................................. 9 Register Details ............................................................................... 42

Pin Configurations and Function Descriptions ......................... 10 GAIN_MUX Register Details ................................................... 42

Typical Performance Characteristics ........................................... 11 Software Reset Register (Reset) Details ................................... 43

Theory of Operation ...................................................................... 23 Clock Synchronization Configuration Register (SYNC_CFG)

Details .......................................................................................... 44

Programmable Gain Instrumentation Amplifier .................. 23

Digital Error Register (DIGITAL_ERR) Details .................... 45

Input Multiplexer ....................................................................... 24

Analog Error Register (ANALOG_ERR) Details .................. 46

EMI Reduction and Internal EMI Filter ................................. 24

GPIO Data Register (GPIO_DATA) Details ......................... 47

Input Amplifier ........................................................................... 25

Internal Mux Control Register (INPUT_MUX) Details ...... 48

Output Amplifier........................................................................ 25

Wire Break Detect Register (WB_DETECT) Details ............ 49

Power Supplies ............................................................................ 26

GPIO Direction Register (GPIO_DIR) Details ..................... 50

ESD Map ...................................................................................... 26

Sequential Chip Select Register (SCS) Details ........................ 50

Output Ripple Calibration Configuration .............................. 27

Analog Error Mask Register (ANALOG_ERR_DIS) Details ... 51

General-Purpose Inputs/Outputs (GPIOs) ............................ 27

Digital Error Mask Register (DIGITAL_ERR_DIS) Details ..... 52

Excitation Currents .................................................................... 27

Special Function Configuration Register (SF_CFG) Details .... 53

External Clock Synchronization .............................................. 28

Error Configuration Register ................................................... 54

Sequential Chip Select (SCS) .................................................... 28

Test Multiplexer Register (TEST_MUX) Details .................. 55

Gain Error Calibration .............................................................. 30

Excitation Current Configuration Register

Wire Break Detection ................................................................ 31 (EX_CURRENT_CFG) Details ................................................ 56

Test Multiplexer ......................................................................... 32 Gain Calibration Registers (GAIN_CALx) Details ............... 57

External Mux Control ................................................................ 32 Trigger Calibration Register (TRIG_CAL) Details ............... 58

Digital Interface .............................................................................. 33 Master Clock Count Register (M_CLK_CNT) Details ......... 58

SPI Interface ................................................................................ 33 DIE Revision Identification Register (DIE_REV_ID) Details

Accessing the ADA4254 Register Map ................................... 33 ....................................................................................................... 58

Checksum Protection ................................................................ 33 Device Identification Registers (PART_ID) Details ............. 58

CRC Calculation ......................................................................... 35 Outline Dimensions ....................................................................... 59

Memory Map Checksum Protection ....................................... 35 Ordering Guide .......................................................................... 59

Read-Only Memory (ROM) Checksum Protection .............. 35

Rev. B | Page 2 of 59

Page3

REVISION HISTORY

Data Sheet ADA4254

REVISION HISTORY

6/2020—Rev. A to Rev. B 11/2019—Rev. 0 to Rev. A

Changes to Figure 10 ............................................................................ 11 Changes to Features Section and General Description Section ....... 1

Changes to Figure 23 ............................................................................ 13 Changes to Static Power Dissipation Parameter, Table 1 ........... 7

Changes to Figure 37 ............................................................................ 16 Changes to 3-Wire RTD With Current Excitation Section ...... 38

Change to Input Multiplexer Section ............................................... 24

Changes to External Clock Synchronization Section ....................... 28

Change to Wire Break Detection Section ........................................... 31 11/2019—Revision 0: Initial Version

Changes to Figure 100 ............................................................................ 36

Change to 3-Wire RTD with Current Excitation Section ............... 38

Change to Table 21 .................................................................................. 49

Change to Bits[7:0], DIE_REV_ID[7:0]—Die Revision

Identification Number Section .......................................................... 58

Rev. B | Page 3 of 59

Page4

SPECIFICATIONS

ADA4254 Data Sheet

SPECIFICATIONS

TA = 25°C, VDDH = 28 V, VSSH = −28 V, AVDD = 5 V, AVSS = 0 V, DVDD = 3.3 V, DVSS = 0 V, VOCM = AVDD/2, and no load,

unless otherwise noted.

Table 1.

Parameter Test Conditions/Comments Min Typ Max Unit

OFFSET VOLTAGE Total offset, referred to input (RTI) =

VOSI + VOSO

Gain

Differential Offset Voltage

Input Offset Voltage (VOSI) ±3 ±14 μV

Output Offset Voltage (VOSO) ±40 ±125 μV

Differential Offset Voltage TA = −40°C to +105°C1, total offset drift,

Drift RTI = VOSI/T + VOSO /T

Gain

VOSI/T ±0.03 ±0.08 μV/°C

VOSO/T ±0.98 ±2.5 μV/°C

Differential Offset Voltage vs. VDDH − VSSH = 10 V to 56 V

VDDH and VSSH (Power

Supply Rejection Ratio

(PSRR)), RTI

Gain (G) = 1/16 V/V 80 90 dB

G = 1 V/V 110 120 dB

G = 128 V/V 140 154 dB

Differential Offset Voltage vs. AVDD − AVSS = 2.7 V to 5.5 V

AVDD (PSRR), RTI

G = 1/16 V/V 66 76 dB

G = 1 V/V 90 100 dB

G = 128 V/V 118 136 dB

Differential Offset vs. External Clock frequency = 0.8 MHz to 1.2 MHz

Clock Frequency, RTI

G = 1/16 V/V ±0.2 μV/kHz

G = 1 V/V ±0.1 μV/kHz

G = 128 V/V ±0.002 μV/kHz

COMMON–MODE REJECTION +IN = −IN = −25 V to +25 V, scaling gain = 1 V/V

RATIO (CMRR), RTI

CMRR to 60 Hz

G = 1/16 V/V 92 102 dB

G = 1 V/V 116 126 dB

G = 128 V/V 140 150 dB

G = 1/16 TA = −40°C to +105°C1 88 dB

G = 1 TA = −40°C to +105°C1 112 dB

G = 128 TA = −40°C to +105°C1 136 dB

Rev. B | Page 4 of 59

Page5

Data Sheet ADA4254

Parameter Test Conditions/Comments Min Typ Max Unit

GAIN Output voltage (V ) = 8.5 V p-p2

OUT

Input Gain Range 1/16 to 128 V/V

Output Gain Range 1, 1.25, 1.375 V/V

Gain Error

Before Calibration All Gains <±0.06 ±0.12 %

Using Calibration All Gains <±0.01 ±0.025 %

Coefficient

All Gain Values Except as TA = −40°C to +105°C1 <±0.3 ±1 ppm/°C

Follows:

G = 1/16 V/V, All Scaling T = −40°C to +105°C1

A ±0.8 ±1.5 ppm/°C

Gains

G = 32 V/V, 64 V/V, All TA = −40°C to +105°C1 ±0.4 ±1.5 ppm/°C

Scaling Gains

G = 128 V/V, Scaling Gains TA = −40°C to +105°C1 ±0.6 ±2 ppm/°C

1 V/V, 1.25 V/V

G = 128 V/V, Scaling Gain TA = −40°C to +105°C1 ±0.7 ±2.5 ppm/°C

1.375 V/V

Nonlinearity All gains except 32 V/V, 64 V/V and 128 V/V2, 3 5 15 ppm

G = 32 V/V 7.5 ppm

G = 64 V/V 12 ppm

G = 128 V/V 15 ppm

NOISE 2

Total noise, RTI = e 2 eno

ni Gain

Voltage Noise, 1 kHz, RTI

Input Noise (eni) 17 nV/√Hz

Output Noise (eno) 253 nV/√Hz

0.1 Hz to 10 Hz, RTI

G = 1/16 V/V 95 μV p-p

G = 1 V/V 5.75 μV p-p

G = 128 V/V 330 nV p-p

0.01 Hz to 10 Hz, RTI

G = 1/16 V/V 100 μV p-p

G = 1 V/V 6.8 μV p-p

G = 128 V/V 395 nV p-p

Current Noise

10 Hz 100 fA/√Hz

0.1 Hz to 10 Hz 3.1 pA p-p

0.01 Hz to 10 Hz 4 pA p-p

INPUT CHARACTERISTICS

Input Bias Current ±0.45 ±1.5 nA

TA = −40°C to +85°C1 ±4 nA

TA = −40°C to +105°C1 ±14 nA

Input Offset Current ±0.2 ±1.3 nA

TA = −40°C to +85°C1 ±2.5 nA

TA = −40°C to +105°C1 ±3.5 nA

Input Impedance Common mode >1||11 GΩ||pF

Differential >1||4.7 GΩ||pF

Input Operating Voltage Range Guaranteed by CMRR VSSH + 3 VDDH − 3 V

MUX_OVER_VOLT_ERR

Positive Threshold VDDH − 0.9 V

Negative Threshold VSSH + 0.9 V

INPUT_ERR/GAIN_RST

Positive Threshold VDDH − 1.5 V

Negative Threshold VSSH + 1.5 V

Rev. B | Page 5 of 59

Page6

ADA4254 Data Sheet

Parameter Test Conditions/Comments Min Typ Max Unit

ANALOG OUTPUTS

Output Voltage Swing from AVDD = 5 V, load resistor (RL) = 2.49 kΩ to 2.5 V AVSS + 0.06 AVDD − V

Each Rail 0.08

AVDD = 2.7 V, RL = 1.8 kΩ to 1.35 V AVSS + 0.05 AVDD − V

0.06

Capacitive Load Drive 500 pF

Short-Circuit Current To 2.5 V, G = 1.375, AVDD = 2.7 V to 5 V 3.5 11 25 mA

OUTPUT_ERR

Positive Threshold AVDD − 0.03 V

Negative Threshold AVSS + 0.03 V

VOCM DYNAMIC PERFORMANCE

−3 dB Bandwidth 2.3 MHz

Slew Rate 1.9 V/μs

Voltage Noise Frequency = 1 kHz 160 nV/√Hz

Gain 1 V/V

VOCM INPUT CHARACTERISTICS

Input Voltage Range AVSS AVDD − 1 V

Input Resistance 10 GΩ

Common Mode Offset Voltage 20 μV

Common Mode Offset 2.5 μV/°C

Voltage Drift

Input Bias Current 500 pA

DYNAMIC RESPONSE

Small Signal ±3 dB Bandwidth

G = 1/16 V/V 15 kHz

G = 1/8 V/V 28 kHz

G = 1/4 V/V 67 kHz

G = 1/2 V/V 138 kHz

G = 1 V/V 1800 kHz

G = 2 V/V 513 kHz

G = 4 V/V 341 kHz

G = 8 V/V 319 kHz

G = 16 V/V 297 kHz

G = 32 V/V 275 kHz

G = 64 V/V 257 kHz

G = 128 V/V 209 kHz

Settling Time 0.01% VOUT = 8 V p-p

G = 1 V/V 10 μs

G = 8 V/V 8 μs

G = 128 V/V 5 μs

Settling Time 0.0015% (16-Bit) VOUT = 8 V p-p

G = 1 V/V 18 μs

G = 8 V/V 15 μs

G = 128 V/V 15 μs

Slew Rate VOUT = 8 V p-p2

G = 1/16 V/V 0.06 V/μs

G = 1 V/V 0.8 V/μs

G = 128 V/V 3.1 V/μs

Rev. B | Page 6 of 59

Page7

Data Sheet ADA4254

Parameter Test Conditions/Comments Min Typ Max Unit

THD VOUT = 8 V p-p at frequency = 1 kHz

G = 1 V/V −104 dB

G = 8 V/V −96 dB

G = 128 V/V −80 dB

Input Overload Recovery Time Input voltage (VIN) = 56 V p-p 40 μs

Output Overload Recovery G = 1 V/V, VIN = 10 V p-p 6 μs

Time

EXCITATION CURRENT SOURCES

(IOUT_LV/IOUT_HV)

Output Current Range 100 1500 μA

Initial Tolerance ±3 ±10 %

Drift TA = −40°C to +105°C ±200 ppm/°C

Current Matching ±3 ±8 %

Drift Matching TA = −40°C to +105°C ±50 ppm/°C

WIRE BREAK CURRENTS

Output Current Range 0.25 16 μA

Impedance Threshold (VDDH − 4)/I 4

WB Ω

Initial Tolerance ±12 %

Drift TA = −40°C to +105°C ±250 ppm/°C

DIGITAL INPUTS

Low (VINL) 0 0.8 V

High (VINH) 0.6 × DVDD DVDD V

Digital Input Pin Capacitance 5 pF

DIGITAL OUTPUT

Low (VOL) Sinking 4 mA 0.7 V

High (VOH) Sourcing 2 mA DVDD − 0.8 V

INTERNAL/EXTERNAL CLOCK

Internal Clock

Frequency 0.8 1 1.2 MHz

Duty Cycle 50 %

Internal Clock Divider Range 1 32 MHz/

MHz

POWER SUPPLY

VDDH − VSSH 10 56 V

AVDD − AVSS 2.7 5 V

DVDD − DVSS 2.7 5 V

IVDDH 600 765 μA

IVSSH 780 985 μA

IDVDD DVDD = 3 V 150 205 μA

IAVDD 980 1305 μA

Static Power Dissipation DVDD = 3 V, VSSH = −28 V, VDHH = 28 V 44 56 mW

DVDD = 3 V, VSSH = −15 V, VDDH = 15 V 26 34 mW

DVDD = 3 V, VSSH = −12 V, VDDH = 12 V 22 28 mW

1 Guaranteed by design. These specifications are not production tested but are supported by characterization data at the initial product release.

2 For gains less than 1/2, a smaller output swing is used.

3 Only G = 1 V/V is production tested.

4 IWB means wire break current.

Rev. B | Page 7 of 59

Page8

TIMING SPECIFICATIONS、Timing Diagrams

ADA4254 Data Sheet

TIMING SPECIFICATIONS

VDDH = 28 V, VSSH = −28 V, AVDD = 5 V, AVSS = 0 V, DVDD = 3.3 V, DVSS = 0 V, VOCM = AVDD/2 V.

Table 2. Digital Values and SPI Timing Specifications

Parameter Test Conditions/Comments Min Typ Max Unit

Maximum Clock Rate (SCLK) 5 MHz

Minimum Pulse Width (SCLK)

High tPWH 75 ns

Low tPWL 75 ns

SDI/SDO to SCLK Setup Time tDS 10 ns

SDI/SDO to SCLK Hold Time tDH 10 ns

Data Valid, SDO to SCLK tDV 50 ns

Setup Time, CS to SCLK tDCS 30 ns

Timing Diagrams

INSTRUCTION CYCLE DATA TRANSFER CYCLE

CS

SCLK

SDIO R/W A6 A5 A4 A3 A2 A1 A0 D7N D6N D5N D30 D20 D10 D00

SDO D7N D6N D5N D30 D20 D10 D00

Figure 2. SPI Timing Diagram, MSB First

tDCS

tSCLK

CS

tPWH tPWL

SCLK

tDS tDH

SDI INSTRUCTION BIT 7 INSTRUCTION BIT 6

Figure 3. SPI Register Write Timing Diagram

CS

SCLK

tDV

SDI, DATA BIT n DATA BIT n – 1

SDO

Figure 4. SPI Register Read Timing Diagram

Rev. B | Page 8 of 59

15741-004 15741-003 15741-002

Page9

ABSOLUTE MAXIMUM RATINGS、THERMAL RESISTANCE、ESD CAUTION

Data Sheet ADA4254

ABSOLUTE MAXIMUM RATINGS

Table 3. THERMAL RESISTANCE

Parameter Rating Thermal performance is directly linked to printed circuit board

VDDH VSSH – 0.3 V to VSSH + 60 V (PCB) design and operating environment. Careful attention to

AVDD AVSS – 0.3 V to AVSS + 5.5 V PCB thermal design is required.

DVDD DVSS – 0.3 V to DVSS + 5.5 V θJA is the natural convection, junction to ambient, thermal

AVSS or DVSS VSSH – 0.3 V to VSSH + 30 V resistance measured in a one cubic foot sealed enclosure. θJC

Voltage VDDH – 30 V to VDDH + 0.3 V is the junction to case thermal resistance.

Current ±10 mA

Input Voltage (+IN1, −IN1, +IN2, VSSH − 60 V to VSSH + 60 V Table 4. Thermal Resistance

or −IN2) Package Type1 θJA θJC Unit

Differential Input Voltage 60 V CP-28-10 36.9 1.9 °C/W

Between Any Two Amplifier RU-24 64.8 14.11 °C/W

Inputs (+IN1, −IN1, +IN2, or

−IN2) 1 The thermal resistance values specified in Table 4 are simulated based on

−OUT, +OUT Short-Circuit Indefinite JEDEC specifications (unless specified otherwise) and must be used in

compliance with JESD51-12.

Current

VOCM Refer to the ESD Map section for a schematic of ESD diodes

Voltage AVSS – 0.3 V to AVDD + 0.3 V and paths.

Current ±10 mA ESD CAUTION

Digital Inputs/Outputs (SPI and DVSS – 0.3 V to DVDD + 0.3 V

GPIO), Voltage

Digital Inputs (SPI and GPIO), ±10 mA

Current

IOUT_LV

Voltage AVSS – 0.3 V to AVDD + 0.3 V

Current ±10 mA

IOUT_HV

Voltage VSSH – 0.3 V to VDDH + 0.3 V

Current ±10 mA

Operating Temperature Range −40°C to +125°C

Specified Temperature Range −40°C to +105°C

Maximum Junction Temperature +150°C

Storage Temperature Range −65°C to +150°C

Stresses at or above those listed under Absolute Maximum Ratings

may cause permanent damage to the product. This is a stress rating

only; functional operation of the product at these or any other

conditions above those indicated in the operational section of this

specification is not implied. Operation beyond the maximum

operating conditions for extended periods may affect product

reliability.

Rev. B | Page 9 of 59

Page10

PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

ADA4254 Data Sheet

PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

–OUT 1 24 +OUT

VOCM 2 23 GPIO0

AVSS 3 22 GPIO1

AVDD 4 21 GPIO2

+IN1 1 21 VOCM

IOUT_LV 5 20 GPIO3

–IN1 2 20 –OUT

+IN2 3 19 +OUT IOUT_HV 6 ADA4254 19 GPIO4

ADA4254 TOP VIEW

–IN2 4 18 GPIO0 VDDH 7 18 CS

DNC 5 TOP VIEW 17 GPIO1

EPAD VSSH 8 17 SCLK

DVSS 6 16 GPIO2

+IN1 9 16 SDI

DVDD 7 15 GPIO3

–IN1 10 15 SDO

+IN2 11 14 DVDD

–IN2 12 13 DVSS

NOTES

1. DNC = DO NOT CONNECT. DO NOT CONNECT

TO THIS PIN.

2. CONNECT THE EXPOSED PAD (EPAD)

TO VSSH.

Figure 5. 28-Lead LFCSP Pin Configuration Figure 6. 24-Lead TSSOP Pin Configuration

Table 5. Pin Function Descriptions

Mnemonic LFCSP Pin No. TSSOP Pin No. Description

+IN1 1 9 Channel 1 Positive Input.

−IN1 2 10 Channel 1 Negative Input.

+IN2 3 11 Channel 2 Positive Input.

−IN2 4 12 Channel 2 Negative Input.

DNC 5, 28 Not applicable Do Not Connect. Do not connect to this pin.

DVSS 6 13 Negative Digital Supply Voltage.

DVDD 7 14 Positive Digital Supply Voltage.

SDO 8 15 SPI Serial Data Output.

SDI 9 16 SPI Serial Data Input.

SCLK 10 17 SPI Serial Clock Input.

CS 11 18 SPI Chip Select Input.

GPIO6 12 Not applicable GPIO6/SCS6.

GPIO5 13 Not applicable GPIO5/SCS5.

GPIO4 14 19 GPIO4/SCS4/Clock Input or Output.

GPIO3 15 20 GPIO3/SCS3/Fault Interrupt Output.

GPIO2 16 21 GPIO2/SCS2/Calibration Busy Out.

GPIO1 17 22 GPIO1/SCS1/External Multiplexer Control 1.

GPIO0 18 23 GPIO0/SCS0/External Multiplexer Control 0.

+OUT 19 24 Positive Output.

−OUT 20 1 Negative Output.

VOCM 21 2 Output Amplifier Common-Mode Voltage Input. This pin is high impedance

and is not internally biased.

AVSS 22 3 Output Amplifier Negative Supply Voltage.

AVDD 23 4 Output Amplifier Positive Supply Voltage.

IOUT_LV 24 5 Low Voltage Excitation Current Source Output.

IOUT_HV 25 6 High Voltage Excitation Current Source Output.

VDDH 26 7 Positive High Voltage Supply.

VSSH 27 8 Negative High Voltage Supply.

EPAD Not applicable Exposed Pad. Connect the exposed pad (EPAD) to VSSH.

Rev. B | Page 10 of 59

SDO 8 28 DNC

SDI 9 27 VSSH

SCLK 10 26 VDDH

CS 11 25 IOUT_HV

GPIO6 12 24 IOUT_LV

GPIO5 13 23 AVDD

GPIO4 14 22 AVSS

15741-006

15741-007

Page11

TYPICAL PERFORMANCE CHARACTERISTICS

Data Sheet ADA4254

TYPICAL PERFORMANCE CHARACTERISTICS

TA = 25°C, VDDH = 28 V, VSSH = −28 V, AVDD = 5 V, AVSS = 0 V, DVDD = 3.3 V, DVSS = 0 V, VOCM = AVDD/2, and no load,

unless otherwise noted.

50 50

N = 120 UNITS N = 120 UNITS

45 µ = 0.24µV 45 µ = –11.4nV/°C

σ = 2.4µV σ = 15.7nV/°C

40 40 TA = –40°C TO +105°C

35 35

30 30

25 25

20 20

15 15

10 10

5 5

0 0

–10 –8 –6 –4 –2 0 2 4 6 8 10 –80 –64 –48 –32 –16 0 16 32 48 64 80

OFFSET VOLTAGE (µV) OFFSET VOLTAGE DRIFT (nV/°C)

Figure 7. Offset Voltage Distribution, RTI (Gain = 128 V/V) Figure 10. Offset Voltage Drift Distribution, RTI (Gain = 128 V/V)

50 50

N = 120 UNITS N = 120 UNITS

45 µ = –19.2µV 45 µ = –0.29µV/°C

σ = 22.2µV σ = 0.43µV/°C

40 T = –40°C TO +105°C

40 A

35 35

30 30

25 25

20 20

15 15

10 10

5 5

0 0

–100 –80 –60 –40 –20 0 20 40 60 80 100 –2.0 –1.6 –1.2 –0.8 –0.4 0 0.4 0.8 1.2 1.6 2.0

OFFSET VOLTAGE (µV) OFFSET VOLTAGE DRIFT (µV/°C)

Figure 8. Offset Voltage Distribution, RTI (Gain = 1 V/V) Figure 11. Offset Voltage Drift Distribution, RTI (Gain = 1 V/V)

50 50

N = 120 UNITS N = 120 UNITS

45 µ = –0.34mV 45 µ = –4.84µV/°C

σ = 0.36mV σ = 6.9µV/°C

40 40 TA = –40°C TO +105°C

35 35

30 30

25 25

20 20

15 15

10 10

5 5

0

–2.0 –1.6 –1.2 –0.8 –0.4 0 0.4 0.8 1.2 1.6 2.0 0

–30 –24 –18 –12 –6 0 6 12 18 24 30

OFFSET VOLTAGE (mV) OFFSET VOLTAGE DRIFT (µV/°C)

Figure 9. Offset Voltage Distribution, RTI (Gain = 1/16 V/V) Figure 12. Offset Voltage Drift Distribution, RTI (Gain = 1/16 V/V)

Rev. B | Page 11 of 59

PERCENT OF UNITS (%) PERCENT OF UNITS (%)

PERCENT OF UNITS (%)

15741-127

15741-126 15741-128

PERCENT OF UNITS (%) PERCENT OF UNITS (%) PERCENT OF UNITS (%)

15741-130 15741-129 15741-131

Page12

ADA4254 Data Sheet

0.15 0.15

N = 80 UNITS N = 40 UNITS

1

VOUT (ALL GAINS EXCEPT 1/16V/V) = 8V p-p VOUT (ALL GAINS EXCEPT /16V/V) = 8V p-p

1

V 1

OUT ( /16V/V) = 2V p-p VOUT ( /16V/V) = 2V p-p

0.10 0.10

0.05 0.05

0 0

–0.05 –0.05

–0.10 –0.10

–0.15 –0.15

1/ 1

16 / 1/ 1/ 1 11/ 13

8 4 2 4 /8 2 4 8 16 32 64 128 1/ 1/ 1/ 1 1 3

16 8 4 /2 1 1 /4 1 /8 2 4 8 16 32 64 128

GAIN SETTING (V/V) GAIN SETTING (V/V)

Figure 13. Gain Error vs. Gain Setting Figure 16. Gain Error vs. Gain Setting Using Calibration Coefficients

0.20 0.20

N = 80 UNITS N = 40 UNITS

VOUT (ALL GAINS EXCEPT 1/16V/V) = 8V p-p VOUT (ALL GAINS EXCEPT 1/16V/V) = 8V p-p

0.15 VOUT (1/16V/V) = 2V p-p 0.15 VOUT (1/16V/V) = 2V p-p

0.10 0.10

0.05 0.05

0 0

–0.05 –0.05

–0.10 –0.10

–0.15 –0.15

–0.20 –0.20

1/ 1

16 / 1

8 / 1

4 /2 1 11/ 13

4 /8 2 4 8 16 32 64 128 1/16 1/8 1/4 1/2 1 11/4 13/8 2 4 8 16 32 64 128

GAIN SETTING (V/V) GAIN SETTING (V/V)

Figure 14. Gain Error Distribution vs. Gain Setting Figure 17. Gain Error Distribution vs. Gain Setting Using Calibration

Coefficients

3 0.20

N = 80 UNITS N = 80 UNITS

V 1 1

OUT (ALL GAINS EXCEPT /16V/V) = 8V p-p VOUT (ALL GAINS EXCEPT /16V/V) = 8V p-p

V (1 0.15

OUT /16V/V) = 2V p-p VOUT (1/16V/V) = 2V p-p

2 TA = –40°C TO +105°C

0.10

1

0.05

0 0

–0.05

–1

–0.10

–2

–0.15

–3

1/ 1 1

16 /8 / 1

4 / 1 3

2 1 1 /4 1 /8 2 4 8 16 32 64 128 –0.20

GAIN SETTING (V/V)

GAIN SETTING CHANGE (V/V)

Figure 15. Gain Error Drift vs. Gain Setting Figure 18. Gain Error Deviation Between Sequential Gain Settings

Rev. B | Page 12 of 59

GAIN ERROR (%)

GAIN ERROR DRIFT MEAN ±3σ (ppm/°C) GAIN ERROR MEAN ±3σ (%)

15741-016

15741-013

15741-015

GAIN ERROR (%)

GAIN ERROR MEAN ±3σ (%) GAIN EROR MEAN ±3σ (%)

1/16 TO 1/8

1/ TO 18 /4

1/4 TO 1/2

1/2 TO 1

1 TO 11/4

11/4 TO 13/8

13/8 TO 2

2 TO 4

4 TO 8

8 TO 16

16 TO 32

32 TO 64

64 TO 128

15741-017 15741-218

15741-217

Page13

Data Sheet ADA4254

6 10

GAIN = 1V/V GAIN = 1V/V

5 9

4

8

3

7

2

1 6

0 5

–1 4

–2

3

–3

2

–4

–5 1

–6 0

–5 –4 –3 –2 –1 0 1 2 3 4 5 –40 –20 0 20 40 60 80 100 120

DIFFERENTIAL OUTPUT VOLTAGE (V) TEMPERATURE (°C)

Figure 19. Gain Nonlinearity Figure 22. Gain Nonlinearity vs. Temperature

160 140

GAIN = 128V/V

140 120

GAIN = 1V/V

120 100

GAIN = 1/16V/V

100 80

80 60

60 40

40 20

GAIN = 128V/V

GAIN = 1V/V

20 0 GAIN = 1/16V/V

0 –20

1 10 100 1k 10k 100k 1M 1 10 100 1k 10k 100k 1M

FREQUENCY (Hz) FREQUENCY (Hz)

Figure 20. CMRR vs. Frequency Figure 23. CMRR vs. Frequency with 1 kΩ Imbalance

50 100

N = 4356 UNITS N = 120 UNITS

45 µ = –10.2nV/V 80 TA = –40°C TO +105°C

σ = 7.9nV/V

40 60

35 40

30 20

25 0

20 –20

15 –40

10 –60

5 –80

0 –100

–65 –55 –45 –35 –25 –15 –5 5 15 25 35 45 55 –40 –20 –5 25 85 105

CMRR (nV/V) TEMPERATURE (°C)

Figure 21. CMRR Distribution (Gain = 128 V/V) Figure 24. CMRR Mean vs. Temperature (Gain = 128 V/V)

Rev. B | Page 13 of 59

PERCENT OF UNITS (%)

CMRR (dB) GAIN NONLINEARITY (ppm)

15741-141 15741-219

15741-152

CMRR MEAN ±3σ (nV/V) CMRR (dB) GAIN NONLINEARITY (ppm)

15741-203 15741-140 15741-234

Page14

ADA4254 Data Sheet

50 2.0

N = 4356 UNITS N = 120 UNITS

45 µ = –0.34µV/V TA = –40°C TO +105°C

σ = 0.13µV/V 1.5

40

1.0

35

30 0.5

25 0

20

–0.5

15

–1.0

10

5 –1.5

0 –2.0

–0.95 –0.75 –0.55 –0.35 –0.15 0.05 0.25 –40 –20 –5 25 85 105

CMRR (µV/V) TEMPERATURE (°C)

Figure 25. CMRR Distribution (Gain = 1 V/V) Figure 28. CMRR Mean vs. Temperature (Gain = 1 V/V)

50 20

N = 4356 UNITS N = 120 UNITS

45 µ = –5.8µV/V TA = –40°C TO +105°C

σ = 2.1µV/V 15

40

10

35

5

30

25 0

20

–5

15

–10

10

–15

5

0 –20

–13 –11 –9 –7 –5 –3 –1 1 3 5 7 –40 –20 –5 25 85 105

CMRR (µV/V) TEMPERATURE (°C)

Figure 26. CMRR Distribution (Gain = 1/16 V/V) Figure 29. CMRR Mean vs. Temperature (Gain = 1/16 V/V)

50 50

N = 4356 UNITS N = 4356 UNITS

45 µ = 0.3nA 45 µ = 0.01nA

σ = 0.1nA σ = 0.14nA

40 40

35 35

30 30

25 25

20 20

15 15

10 10

5 5

0 0

–0.05 0.05 0.15 0.25 0.35 0.45 0.55 0.65 0.75 –0.5 –0.3 –0.1 0.1 0.3 0.5 0.7

INPUT BIAS CURRENT (nA) INPUT OFFSET CURRENT (nA)

Figure 27. Input Bias Current Distribution Figure 30. Input Offset Current Distribution

Rev. B | Page 14 of 59

PERCENT OF UNITS (%) PERCENT OF UNITS (%) PERCENT OF UNITS (%)

15741-150

15741-155 15741-151

PERCENT OF UNITS (%) CMRR MEAN ±3σ (µV/V) CMRR MEAN ±3σ (µV/V)

15741-156

15741-202 15741-201

Page15

Data Sheet ADA4254

10 5

N = 15 UNITS N = 15 UNITS

8 4

6 3

4 2

2 1

0 0

–2 –1

–4 –2

–6 –3

–8 –4

–10 –5

–40 –20 0 20 40 60 80 100 120 –40 –20 0 20 40 60 80 100 120

TEMPERATURE (°C) TEMPERATURE (°C)

Figure 31. Input Bias Current vs. Temperature Figure 34. Input Offset Current vs. Temperature

20 10

IB+

IB– 8

15

6

10

4

5

2

0 0

–2

–5

–4

–10

–6

–15

VSSH = –25V –8 VSSH = –25V

VDDH = +25V VDDH = +25V

–20 –10

–24 –20 –16 –12 –8 -4 0 4 8 12 16 20 24 –24 –20 –16 –12 –8 –4 0 4 8 12 16 20 24

INPUT COMMON-MODE VOLTAGE (V) INPUT COMMON-MODE VOLTAGE (V)

Figure 32. Input Bias Current vs. Input Common-Mode Voltage Figure 35. Input Offset Current vs. Input Common-Mode Voltage

20 20

VSSH = –15V VSSH = –5V

VDDH = +15V VDDH = +5V

15 15

10 10

5 5

0 0

±5

±15

–5 –5 OVP OVP

OVP OVP VSSH – 60V VSSH + 60V

VSSH – 60V VSSH + 60V

–10 –10

–15 –15

–20 –20

–90 –75 –60 –45 –30 –15 0 15 30 45 60 –75 –65 –55 –45 –35 –25 –15 –5 5 15 25 35 45 55 65

INPUT VOLTAGE (V) INPUT VOLTAGE (V)

Figure 33. Input Overvoltage Performance, VDDH/VSSH = ±15 V Figure 36. Input Overvoltage Performance, VDDH/VSSH = ±5 V

Rev. B | Page 15 of 59

INPUT BIAS CURRENT (µA)

INPUT BIAS CURRENT (nA) INPUT BIAS CURRENT (nA)

15741-153 15741-211

15741-230

INPUT BIAS CURRENT (µA) INPUT OFFSET CURRENT (nA) INPUT OFFSET CURRENT (nA)

15741-229 15741-154 15741-212

Page16

ADA4254 Data Sheet

30 2.50

GAIN = 128V/V GAIN = 1V/V FROM VDDH

25 FROM VSSH

20 2.25

15

10 GAIN = 1/4V/V 2.00

5

0 GAIN = 1/8V/V 1.75

–5

GAIN = 1/16V/V

–10 1.50

–15

–20 1.25

–25

–30 1.00

–6 –5 –4 –3 –2 –1 0 1 2 3 4 5 6 –40 –20 0 20 40 60 80 100 120

DIFFERENTIAL OUTPUT VOLTAGE (V) TEMPERATURE (°C)

Figure 37. Diamond Plot Figure 40. Input Voltage Headroom vs. Temperature

750 700

VSSH = –28V, VDDH = +28V

VSSH = –5V, VDDH = +5V

700 650

VCM = –25V

650 600

VCM = +25V

600 550

550 500

VCM = 0V

500 450

450 400

–28 –24 –20 –16 –12 –8 –4 0 4 8 12 16 20 24 28 –40 –20 0 20 40 60 80 100 120

INPUT COMMON-MODE VOLTAGE (V) TEMPERATURE (°C)

Figure 38. Multiplexer On-Resistance vs. Input Common-Mode Voltage Figure 41. Multiplexer On-Resistance vs. Temperature

160 160

140 140 GAIN = 128V/V

120

GAIN = 128V/V 120

GAIN = 1V/V

100

GAIN = 1V/V 100

GAIN = 1/16V/V

80

80

60

GAIN = 1/16V/V

60

40

40

20

0 20

–20 0

1 10 100 1k 10k 100k 1M 1 10 100 1k 10k 100k 1M

FREQUENCY (Hz) FREQUENCY (Hz)

Figure 39. VSSH PSRR vs. Frequency Figure 42. VDDH PSRR vs. Frequency

Rev. B | Page 16 of 59

VSSH PSRR (dB) MULTIPLEXER ON-RESISTANCE (Ω) INPUT COMMON-MODE VOLTAGE (V)

15741-149 15741-208 15741-206

MULTIPLEXER ON-RESISTANCE (Ω)

VDDH PSRR (dB) INPUT VOLTAGE HEADROOM (V)

15741-147 15741-157

15741-207

Page17

Data Sheet ADA4254

160 160

GAIN = 128V/V GAIN = 128V/V

140 140

120 120 GAIN = 1V/V

GAIN = 1V/V

100 100 GAIN = 1/16V/V

GAIN = 1/16V/V

80 80

60 60

40 40

20 20

0 0

1 10 100 1k 10k 100k 1M 1 10 100 1k 10k 100k 1M

FREQUENCY (Hz) FREQUENCY (Hz)

Figure 43. AVDD PSRR vs. Frequency Figure 46. DVDD PSRR vs. Frequency

1000 1100

900 AVDD = 5V

800 DVDD = 3V 1000

700 IVDDH IAVDD

600 900

500 800

400

300 700

200

100 600

0

–100 500

–200

–300 400

–400

–500 300

–600 200

–700 IVSSH IDVDD

–800 100 VSSH = –28V

–900 VDDH = +28V

–1000 0

0 5 10 15 20 25 30 35 40 45 50 55 60 65 0 1 2 3 4 5 6

VDDH – VSSH (V) AVVD/DVDD (V)

Figure 44. Quiescent Current vs. Supply Voltage (VDDH – VSSH) Figure 47. Quiescent Current vs. Supply Voltage (AVDD/DVDD)

1050 100

1000 IVSSH

950

900

850

800 IVDDH 10

750 GAIN = 1/16V/V

700

650 IAVDD

600

550 1

500

450 GAIN = 1V/V

400

350 0.10

300

250

200 GAIN = 128V/V

150 IDVDD

100

–40 –20 0 20 40 60 80 100 120 0.01

0.01 0.1 1 10 100 1k 10k 100k

TEMPERATURE (°C) FREQUENCY (Hz)

Figure 45. Quiescent Current vs. Temperature Figure 48. Voltage Noise Spectral Density, RTI

Rev. B | Page 17 of 59

QUIESCENT CURRENT (µA) QUIESCENT CURRENT (µA) AVDD PSRR (dB)

15741-138

15741-227 15741-226

VNOISE (µV/√Hz) QUIESCENT CURRENT (µA) DVDD PSRR (dB)

15741-125 15741-204

15741-225

Page18

ADA4254 Data Sheet

250 250

200 195nV 200 190nV

150 150

100

100

50

50

0 395nV p-p 330nV p-p

0

–50

–50

–100

–150 –100

–140nV

–200 –200nV –150

–250 –200

0 10 20 30 40 50 60 70 80 90 100 0 1 2 3 4 5 6 7 8 9 10

TIME (Seconds) TIME (Seconds)

Figure 49. 0.01 Hz to 10 Hz Voltage Noise, RTI (Gain = 128 V/V) Figure 52. 0.1 Hz to 10 Hz Voltage Noise, RTI (Gain = 128 V/V)

4 4

3.3µV

3 3 3.00µV

2 2

1 1

0 6.8µV p-p 0 5.75µV p-p

–1 –1

–2 –2

–2.75µV

–3 –3

–3.5µV

–4 –4

0 10 20 30 40 50 60 70 80 90 100 0 1 2 3 4 5 6 7 8 9 10

TIME (Seconds) TIME (Seconds)

Figure 50. 0.01 Hz to 10 Hz Voltage Noise, RTI (Gain = 1 V/V) Figure 53. 0.1 Hz to 10 Hz Voltage Noise, RTI (Gain = 1 V/V)

60 60

45µV

40 40 40µV

20 20

0 0

100µV p-p 95µV p-p

–20 –20

–40 –40

–55µV –55µV

–60 –60

0 10 20 30 40 50 60 70 80 90 100 0 1 2 3 4 5 6 7 8 9 10

TIME (Seconds) TIME (Seconds)

Figure 51. 0.01 Hz to 10 Hz Voltage Noise, RTI (Gain = 1/16 V/V) Figure 54. 0.1 Hz to 10 Hz Voltage Noise, RTI (Gain = 1/16 V/V)

Rev. B | Page 18 of 59

VOLTAGE NOISE (µV) VOLTAGE NOISE (µV)

VOLTAGE NOISE (nV)

15741-134

15741-133

15741-132

VOLTAGE NOISE (µV) VOLTAGE NOISE (µV) VOLTAGE NOISE (nV)

15741-135 15741-136 15741-137

Page19

Data Sheet ADA4254

50 6

128V/V

40 GAIN = 1.375V/V

64V/V 3 GAIN = 1.25V/V

30 32V/V GAIN = 1V/V

16V/V

20 0

8V/V

4V/V

10

2V/V –3

0 1V/V

1/2V/V

–10 –6

1/4V/V

1/8

–20 V/V

1/16V/V –9

–30

–40 –12

1 10 100 1k 10k 100k 1M 10M 10 100 1k 10k 100k 1M 10M

FREQUENCY (Hz) FREQUENCY (Hz)

Figure 55. Small Signal Frequency Response Figure 58. VOCM Small Signal Frequency Response

–30 –20

DIFFERENTIAL OUTPUT NOTE: THD + N BECOMES DOMINATED BY

VOLTAGE = 8V p-p NOISE AS OUTPUT SIGNAL SIZE REDUCES

–40 –30

–40

–50

–50

–60 GAIN = 128V/V

GAIN = 128V/V

–60

–70

GAIN = 1/2V/V –70 GAIN = 8V/V

–80

GAIN = 8V/V –80

GAIN = 1V/V

–90 –90 GAIN = 1/2V/V

NOTE: FLAT PORTION OF THE CURVES GAIN = 1V/V

IS DOMINATED BY NOISE INPUT FREQUENCY = 1kHz

–100 –100

10 100 1k 10k 0.1 1 10

FREQUENCY (Hz) DIFFERENTIAL OUTPUT VOLTAGE (V p-p)

Figure 56. Total Harmonic Distortion Plus Noise (THD + N) vs. Frequency with Figure 59. THD + N vs. Differential Output Voltage with 100 kHz Filter,

100 kHz Filter, Differential Load Resistor (RL, DIFF) = 5 kΩ RL, DIFF = 5 kΩ

–30 14

DIFFERENTIAL OUTPUT

VOLTAGE = 8V p-p AVDD = +5V SOURCING

–40 13

–50

12 AVDD = +2.7V SOURCING

–60

GAIN = 128V/V 11

–70 AVDD = +2.7V SINKING

10

–80

9

–90 AVDD = +5V SINKING

GAIN = 8V/V GAIN = 1/2V/V

–100 8

GAIN = 1V/V

–110 7

10 100 1k 10k –40 –20 0 20 40 60 80 100 120

FREQUENCY (Hz) TEMPERATURE (°C)

Figure 57. THD vs. Frequency, RL, DIFF = 5 kΩ Figure 60. Sinking/Sourcing Short-Circuit Output Current vs. Temperature

Rev. B | Page 19 of 59

THD (dB) THD + N (dB) GAIN (dB)

15741-231 15741-232

15741-166

OUTPUT CURRENT (mA) THD + N (dB) GAIN (dB)

15741-213 15741-233

15741-205

Page20

ADA4254 Data Sheet

60 60

N = 4356 UNITS N = 4356 UNITS

µ = 12mA µ = 9mA

σ = 1.3mA σ = 1mA

50 50

40 40

30 30

20 20

10 10

0 0

6 8 10 12 14 16 18 20 4 6 8 10 12 14 16

SHORT-CIRCUIT CURRENT (mA) SHORT-CIRCUIT CURRENT (mA)

Figure 61. Sourcing Short-Circuit Current Distribution Figure 64. Sinking Short-Circuit Current Distribution

–IN1 INPUT SIGNAL –IN1 INPUT SIGNAL

+IN1 = 0V +IN1 = 0V

DIFFERENTIAL DIFFERENTIAL

OUTPUT VOLTAGE OUTPUT VOLTAGE

FAULT INTERRUPT FAULT INTERRUPT

10µs/DIV 10µs/DIV

Figure 62. Large Signal Step Response (Gain = 128 V/V) Figure 65. Large Signal Step Response (Gain = 8 V/V)

– IN1 INPUT SIGNAL – IN1 INPUT SIGNAL

+IN1 = 0V +IN1 = 0V

INPUT

OVERLOADED

DIFFERENTIAL DIFFERENTIAL

OUTPUT VOLTAGE OUTPUT VOLTAGE

FAULT INTERRUPT FAULT INTERRUPT

10µs/DIV 10µs/DIV

Figure 63. Input Overload Recovery Step Response (Gain = 1 V/V) Figure 66. Large Signal Step Response (Gain = 1 V/V)

Rev. B | Page 20 of 59

PERCENT OF UNITS (%)

5V/DIV 5V/DIV 5V/DIV 5V/DIV 5V/DIV 50mV/DIV

15741-169 15741-172

15741-160

PERCENT OF UNITS (%)

5V/DIV 5V/DIV 5V/DIV

5V/DIV 5V/DIV 1V/DIV

15741-171

15741-170

15741-159