1/107ページ

ダウンロード(4.6Mb)

16-Bit, 16-Channel, 500 kSPS/1 MSPS, Easy Drive Multiplexed SAR ADC

このカタログについて

| ドキュメント名 | Data Sheet AD4695/AD4696 |

|---|---|

| ドキュメント種別 | 製品カタログ |

| ファイルサイズ | 4.6Mb |

| 取り扱い企業 | マウザー・エレクトロニクス (この企業の取り扱いカタログ一覧) |

この企業の関連カタログ

このカタログの内容

Page1

Features、Applications、General Description

Data Sheet

AD4695/AD4696

16-Bit, 16-Channel, 500 kSPS/1 MSPS, Easy Drive Multiplexed SAR ADC

FEATURES GENERAL DESCRIPTION

► Easy Drive The AD4695/AD4696 are compact, high accuracy, low power, 16-

► Reduced analog input and reference drive requirements channel, 16-bit, 500 kSPS/1 MSPS, multiplexed input precision,

► On-chip reference buffer (WLCSP only) successive approximation register (SAR) analog-to-digital convert-

► Overvoltage protection up to 5 mA on each analog input ers (ADCs) with Easy Drive features and extensive digital function-

ality.

► Long acquisition phase, ≥71.5% (715 ns/1000 ns) of cycle

time at 1 MSPS The AD4695/AD4696 are optimal for use in space constrained,

► High performance multichannel, precision data acquisition systems and monitoring

► Sample rate: 500 kSPS (AD4695) or 1 MSPS (AD4696) circuits. The AD4695/AD4696 feature a true 16-bit SAR ADC core

INL: ±1.0 LSB maximum with no missing codes, a 16-channel, low crosstalk multiplexer, a

► flexible channel sequencer, overvoltage protection clamp circuits on

► Guaranteed 16-bit, no missing codes each analog input, on-chip oversampling and decimation, threshold

► SINAD: 93 dB typical, fIN = 1 kHz detection and alert indicators, and an autonomous conversion (au-

► Oversampled dynamic range: 111.2 dB, OSR = 64 tocycle) mode.

► Small footprint, high channel density The AD4695/AD4696 Easy Drive features relax the drive require-

► 32-lead 5 mm × 5 mm LFCSP ments of the analog front end (AFE) and reference circuitry. Analog

► 36-ball 2.96 mm × 2.96 mm WLCSP input high-Z mode and reference input high‑Z mode simplify system

► Easy Drive features support system level designs with fewer designs, reduce component count, and increase channel density

components by removing the need for dedicated high speed ADC drivers and

► Enhanced digital functionality reference buffers. The WLCSP option of the AD4695/AD4696 in-

► First conversion accurate, no latency or pipeline delay cludes an internal reference buffer, which provides a true, buffered

► Fast conversion time and dual-/quad-SDO modes allow low reference input.

SPI clock rates Input overvoltage protection clamps on each analog input protect

► Customizable channel sequencer the AD4695/AD4696 from overvoltage events and prevent overvolt-

► On-chip oversampling and decimation age events on one channel from degrading performance on other

Threshold detection alerts channels (see Figure 27).

►

► Offset and gain correction Advanced digital functionality makes the AD4695/AD4696 compati-

► Autonomous conversion (autocycle) mode ble with a variety of low power digital hosts. The low serial periph-

1.14 V to 1.98 V logic SPI eral interface (SPI) clock rate requirements, on-chip customizable

► channel sequencers, and oversampling and decimation reduce the

► Low power burden on the digital host system. Autocycle mode and threshold

► 8 mW at fS = 1 MSPS and 4 mW at fS = 500 kSPS detection features enable low power, interrupt driven firmware de-

► 4 µW standby power dissipation with the internal LDO disa- sign by performing conversions autonomously and generating alerts

bled based on channel specific threshold limits.

► Internal LDO enables 3.15 V to 5.5 V, single analog supply

operation The AD4695/AD4696 are available in a 5 mm × 5 mm 32-lead

lead frame chip scale package (LFCSP) and a 2.96 mm × 2.96

► Wide operating temperature range: −40°C to +125°C mm 36-ball wafer level chip scale package (WLCSP) with operation

APPLICATIONS specified from −40°C to +125°C.

► Photodiode monitoring

► Medical instrumentation

► Vital signs monitoring

► Electronic test and measurement

► Automated test equipment

► Instrumentation and process control

► Battery-powered equipment

Rev. A

DOCUMENT FEEDBACK Information furnished by Analog Devices is believed to be accurate and reliable "as is". However, no responsibility is assumed by Analog

Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to

change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and

TECHNICAL SUPPORT registered trademarks are the property of their respective owners.

Page2

Data Sheet AD4695/AD4696

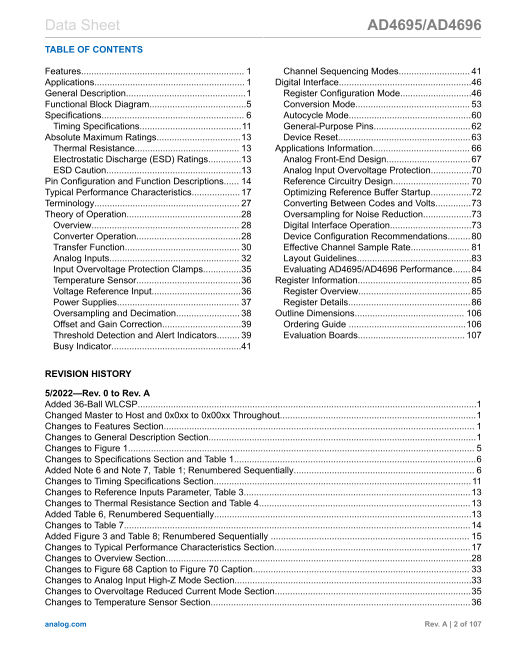

TABLE OF CONTENTS

Features................................................................ 1 Channel Sequencing Modes............................ 41

Applications........................................................... 1 Digital Interface....................................................46

General Description...............................................1 Register Configuration Mode............................46

Functional Block Diagram......................................5 Conversion Mode............................................. 53

Specifications........................................................ 6 Autocycle Mode................................................60

Timing Specifications........................................11 General-Purpose Pins......................................62

Absolute Maximum Ratings.................................13 Device Reset....................................................63

Thermal Resistance......................................... 13 Applications Information...................................... 66

Electrostatic Discharge (ESD) Ratings.............13 Analog Front-End Design.................................67

ESD Caution.....................................................13 Analog Input Overvoltage Protection................70

Pin Configuration and Function Descriptions...... 14 Reference Circuitry Design.............................. 70

Typical Performance Characteristics................... 17 Optimizing Reference Buffer Startup................72

Terminology......................................................... 27 Converting Between Codes and Volts..............73

Theory of Operation.............................................28 Oversampling for Noise Reduction...................73

Overview.......................................................... 28 Digital Interface Operation................................73

Converter Operation.........................................28 Device Configuration Recommendations.........80

Transfer Function............................................. 30 Effective Channel Sample Rate....................... 81

Analog Inputs................................................... 32 Layout Guidelines.............................................83

Input Overvoltage Protection Clamps...............35 Evaluating AD4695/AD4696 Performance.......84

Temperature Sensor.........................................36 Register Information............................................ 85

Voltage Reference Input...................................36 Register Overview............................................85

Power Supplies................................................ 37 Register Details................................................86

Oversampling and Decimation......................... 38 Outline Dimensions........................................... 106

Offset and Gain Correction...............................39 Ordering Guide ..............................................106

Threshold Detection and Alert Indicators......... 39 Evaluation Boards.......................................... 107

Busy Indicator...................................................41

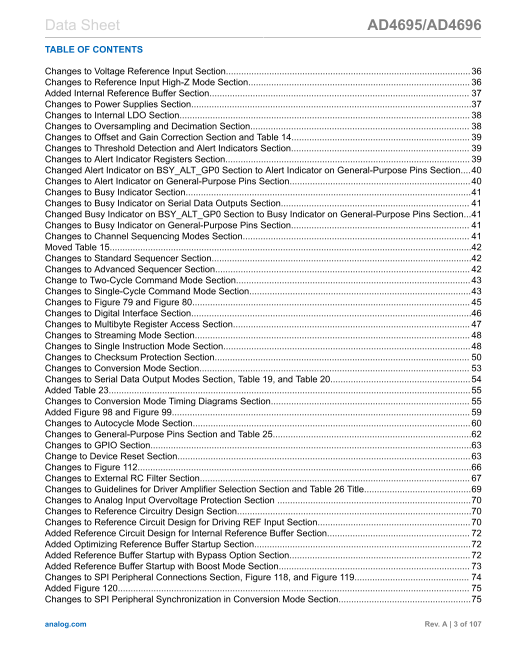

REVISION HISTORY

5/2022—Rev. 0 to Rev. A

Added 36-Ball WLCSP.....................................................................................................................................1

Changed Master to Host and 0x0xx to 0x00xx Throughout.............................................................................1

Changes to Features Section.......................................................................................................................... 1

Changes to General Description Section.........................................................................................................1

Changes to Figure 1........................................................................................................................................ 5

Changes to Specifications Section and Table 1...............................................................................................6

Added Note 6 and Note 7, Table 1; Renumbered Sequentially....................................................................... 6

Changes to Timing Specifications Section.....................................................................................................11

Changes to Reference Inputs Parameter, Table 3.........................................................................................13

Changes to Thermal Resistance Section and Table 4...................................................................................13

Added Table 6, Renumbered Sequentially.....................................................................................................13

Changes to Table 7........................................................................................................................................14

Added Figure 3 and Table 8; Renumbered Sequentially .............................................................................. 15

Changes to Typical Performance Characteristics Section.............................................................................17

Changes to Overview Section........................................................................................................................28

Changes to Figure 68 Caption to Figure 70 Caption..................................................................................... 33

Changes to Analog Input High-Z Mode Section.............................................................................................33

Changes to Overvoltage Reduced Current Mode Section.............................................................................35

Changes to Temperature Sensor Section......................................................................................................36

analog.com Rev. A | 2 of 107

Page3

Data Sheet AD4695/AD4696

TABLE OF CONTENTS

Changes to Voltage Reference Input Section................................................................................................36

Changes to Reference Input High-Z Mode Section....................................................................................... 36

Added Internal Reference Buffer Section...................................................................................................... 37

Changes to Power Supplies Section..............................................................................................................37

Changes to Internal LDO Section.................................................................................................................. 38

Changes to Oversampling and Decimation Section...................................................................................... 38

Changes to Offset and Gain Correction Section and Table 14...................................................................... 39

Changes to Threshold Detection and Alert Indicators Section...................................................................... 39

Changes to Alert Indicator Registers Section................................................................................................ 39

Changed Alert Indicator on BSY_ALT_GP0 Section to Alert Indicator on General-Purpose Pins Section....40

Changes to Alert Indicator on General-Purpose Pins Section.......................................................................40

Changes to Busy Indicator Section................................................................................................................41

Changes to Busy Indicator on Serial Data Outputs Section.......................................................................... 41

Changed Busy Indicator on BSY_ALT_GP0 Section to Busy Indicator on General-Purpose Pins Section...41

Changes to Busy Indicator on General-Purpose Pins Section...................................................................... 41

Changes to Channel Sequencing Modes Section......................................................................................... 41

Moved Table 15..............................................................................................................................................42

Changes to Standard Sequencer Section......................................................................................................42

Changes to Advanced Sequencer Section.................................................................................................... 42

Change to Two-Cycle Command Mode Section............................................................................................43

Changes to Single-Cycle Command Mode Section.......................................................................................43

Changes to Figure 79 and Figure 80............................................................................................................. 45

Changes to Digital Interface Section..............................................................................................................46

Changes to Multibyte Register Access Section............................................................................................. 47

Changes to Streaming Mode Section............................................................................................................ 48

Changes to Single Instruction Mode Section.................................................................................................48

Changes to Checksum Protection Section.................................................................................................... 50

Changes to Conversion Mode Section.......................................................................................................... 53

Changes to Serial Data Output Modes Section, Table 19, and Table 20.......................................................54

Added Table 23..............................................................................................................................................55

Changes to Conversion Mode Timing Diagrams Section.............................................................................. 55

Added Figure 98 and Figure 99..................................................................................................................... 59

Changes to Autocycle Mode Section.............................................................................................................60

Changes to General-Purpose Pins Section and Table 25..............................................................................62

Changes to GPIO Section..............................................................................................................................63

Change to Device Reset Section...................................................................................................................63

Changes to Figure 112...................................................................................................................................66

Changes to External RC Filter Section.......................................................................................................... 67

Changes to Guidelines for Driver Amplifier Selection Section and Table 26 Title..........................................69

Changes to Analog Input Overvoltage Protection Section ............................................................................70

Changes to Reference Circuitry Design Section............................................................................................70

Changes to Reference Circuit Design for Driving REF Input Section............................................................70

Added Reference Circuit Design for Internal Reference Buffer Section........................................................ 72

Added Optimizing Reference Buffer Startup Section.....................................................................................72

Added Reference Buffer Startup with Bypass Option Section....................................................................... 72

Added Reference Buffer Startup with Boost Mode Section........................................................................... 73

Changes to SPI Peripheral Connections Section, Figure 118, and Figure 119............................................. 74

Added Figure 120.......................................................................................................................................... 75

Changes to SPI Peripheral Synchronization in Conversion Mode Section....................................................75

analog.com Rev. A | 3 of 107

Page4

Data Sheet AD4695/AD4696

TABLE OF CONTENTS

Changes to Figure 121 and Figure 122......................................................................................................... 76

Changes to Figure 123 and Figure 124......................................................................................................... 77

Added Figure 125.......................................................................................................................................... 78

Changes to SPI Peripheral Synchronization in Autocycle Mode Section...................................................... 78

Changes to Conversion Mode SPI Clock Frequency Requirements Section and Table 28...........................79

Changes to Device Configuration Recommendations Section...................................................................... 80

Changes to Effective Channel Sample Rate Section.....................................................................................81

Changes to Layout Guidelines Section..........................................................................................................83

Changes to Reference Control Register Figure and Table 49....................................................................... 96

Changes to GPIO Enable Register Figure and Table 53............................................................................... 99

Changes to General-Purpose Pin Function Control Register Figure and Table 54..................................... 100

Changes to Table 55....................................................................................................................................101

Updated Outline Dimensions....................................................................................................................... 106

Changes to Ordering Guide.........................................................................................................................106

Added Evaluation Boards............................................................................................................................ 107

12/2020—Revision 0: Initial Version

analog.com Rev. A | 4 of 107

Page5

Functional Block Diagram

Data Sheet AD4695/AD4696

FUNCTIONAL BLOCK DIAGRAM

Figure 1.

analog.com Rev. A | 5 of 107

Page6

Specifications

Data Sheet AD4695/AD4696

SPECIFICATIONS

AVDD = 3.15 V to 5.5 V, LDO_IN = 2.4 V to 5.5 V with internal LDO enabled, LDO_IN = AGND with internal low dropout (LDO) disabled,

VDD = 1.71 V to 1.89 V with internal LDO disabled, VIO = 1.14 V to 1.98 V, AGND = REFGND = IOGND = 0 V, reference voltage (VREF)

= 2.4 V to 5.1 V, REF = VREF with internal reference buffer disabled, REFIN = VREF with internal reference buffer enabled, reference buffer

boost mode enabled, sample rate (fS) = 1 MSPS for the AD4696, fS = 500 kSPS for the AD4695, input frequency (fIN) = 1 kHz, digital output

load capacitance = 20 pF, autocycle mode disabled, analog input high-Z mode enabled, reference input high-Z mode enabled, busy indicator

and alert indicator not enabled on general-purpose pins, no active overvoltage protection clamps, and TA = −40°C to +125°C, unless otherwise

noted.

Table 1.

Parameter Test Conditions/Comments Min Typ Max Unit

RESOLUTION 16 Bits

ANALOG INPUT1, 2

Input Voltage Range Positive ADC input voltage (IN+) – negative ADC input

voltage (IN−)

Unipolar Mode 0 +VREF V

Pseudobipolar Mode −VREF/2 +VREF/2 V

Operating Input Voltage

IN+ − REFGND IN− = REFGND 0 +VREF V

IN− = COM, odd numbered input −0.1 VREF + 0.1 V

IN− − REFGND IN− = COM, odd numbered input

Unipolar mode −0.1 VREF + 0.1 V

Pseudobipolar mode VREF/2 – 0.1 VREF/2 VREF/2 + 0.1 V

Common-Mode Rejection Ratio (CMRR) fIN = 250 kHz, IN− = COM, odd numbered input 69.5 dB

Analog Input Leakage Current3 10 nA

SAMPLING DYNAMICS

Sample Rate Autocycle mode disabled

AD4695 500 kSPS

AD4696 1 MSPS

Autocycle Sample Period Autocycle mode enabled

AC_CYC = 0x0 8.5 10 11.5 μs

AC_CYC = 0x1 17 20 23 μs

AC_CYC = 0x2 34 40 46 μs

AC_CYC = 0x3 68 80 92 μs

AC_CYC = 0x4 85 100 115 μs

AC_CYC = 0x5 170 200 230 μs

AC_CYC = 0x6 340 400 460 μs

AC_CYC = 0x7 680 800 920 μs

Aperture Delay 2 ns

Aperture Jitter 0.5 ps rms

DC ACCURACY

No Missing Codes 16 Bits

Integral Nonlinearity Error (INL) VREF = 5 V, oversampling ratio (OSR) = 1

LFCSP, TA = −40°C to +125°C −1 ±0.4 +1 LSB

WLCSP, TA = 0°C to +70°C −2 ±0.4 +2 LSB

WLCSP, TA = −40°C to +125°C −2.5 ±0.4 +2.5 LSB

Differential Nonlinearity Error (DNL) VREF = 5 V, OSR = 1 −0.6 ±0.3 +0.6 LSB

Transition Noise VREF = 5 V 0.5 LSB rms

Offset Error4 VREF = 5 V

TA = 25°C ±0.03 mV

TA = −40°C to +125°C −0.43 +0.43 mV

analog.com Rev. A | 6 of 107

Page7

Data Sheet AD4695/AD4696

SPECIFICATIONS

Table 1.

Parameter Test Conditions/Comments Min Typ Max Unit

Offset Error Match4 VREF = 5 V

TA = 25°C ±0.025 mV

TA = −40°C to +125°C −0.23 +0.23 mV

Gain Error4 VREF = 5 V

TA = 25°C ±0.001 %FS5

TA = −40°C to +125°C −0.025 +0.025 %FS

Gain Error Match4 VREF = 5 V

TA = 25°C ±0.002 %FS

TA = −40°C to +125°C −0.012 +0.012 %FS

AC PERFORMANCE

Dynamic Range VREF = 5 V

OSR = 1 93.4 dB

OSR = 4 99.3 dB

OSR = 16 105.3 dB

OSR = 64 111.2 dB

Input RMS Noise OSR = 1 37.8 μV rms

OSR = 4 19.2 μV rms

OSR = 16 9.6 μV rms

OSR = 64 4.9 μV rms

1/f Noise Bandwidth = 0.1 Hz to 10 Hz 5 μV p-p

Signal-to-Noise Ratio (SNR) VREF = 5 V, fIN = 1 kHz 91.25 93 dB

VREF = 4.096 V, fIN = 1 kHz 91.3 dB

VREF = 2.5 V, fIN = 1 kHz 87 dB

Total Harmonic Distortion (THD) VREF = 5 V, fIN = 1 kHz −117 dB

VREF = 4.096 V, fIN = 1 kHz −117.5 dB

VREF = 2.5 V, fIN = 1 kHz −119 dB

Signal-to-Noise-and-Distortion (SINAD)

LFCSP VREF = 5 V, fIN = 1 kHz 91.1 93 dB

VREF = 4.096 V, fIN = 1 kHz 91.3 dB

VREF = 2.5 V, fIN = 1 kHz 87 dB

WLCSP VREF = 5 V, fIN = 1 kHz 89 93 dB

Spurious-Free Dynamic Range (SFDR) VREF = 5 V 121 dB

Channel to Channel Isolation fIN = 100 kHz

LFCSP option −123 dB

WLCSP option −120 dB

Channel to Channel Memory fIN = 100 kHz, fS = 1 MSPS −100 dB

fIN = 100 kHz, fS = 500 kSPS −110 dB

−3 dB Input Bandwidth 11.7 MHz

REFERENCE INPUT6

VREF Range REF input, internal reference buffer disabled 2.4 AVDD + 0.25 V

REFIN input, internal reference buffer disabled REF

REFIN input, internal reference buffer enabled 2.4 AVDD – 0.3 V

REF Leakage Current VREF = 5 V

LFCSP No active overvoltage protection clamps 165 nA

All clamps active, overvoltage reduced, current mode 375 μA

disabled

All clamps active, overvoltage reduced, current mode 8 μA

enabled

WLCSP Internal reference buffer disabled 165 nA

analog.com Rev. A | 7 of 107

Page8

Data Sheet AD4695/AD4696

SPECIFICATIONS

Table 1.

Parameter Test Conditions/Comments Min Typ Max Unit

REF Average Input Current VREF = AVDD = 5 V, internal reference buffer disabled

Reference High-Z Mode Disabled fS = 10 kSPS, unipolar mode 3.3 μA

fS = 500 kSPS, unipolar mode 160 μA

fS = 1 MSPS, unipolar mode 320 µA

fS = 10 kSPS, pseudobipolar mode 4.0 μA

fS = 500 kSPS, pseudobipolar mode 195 μA

fS = 1 MSPS, pseudobipolar mode 390 µA

Reference High-Z Mode Enabled fS = 10 kSPS, unipolar mode 0.3 μA

fS = 500 kSPS, unipolar mode 6 μA

fS = 1 MSPS, unipolar mode 12 μA

fS = 10 kSPS, pseudobipolar mode 0.4 μA

fS = 500 kSPS, pseudobipolar mode 11 μA

fS = 1 MSPS, pseudobipolar mode 22 µA

REFIN Current VREF = 5 V

Internal Reference Buffer Enabled No active overvoltage protection clamps 16 nA

All clamps active, overvoltage reduced, current mode 200 µA

disabled

All clamps active, overvoltage reduced, current mode 4.5 µA

enabled

REFIN Input Capacitance WLCSP, internal reference buffer enabled 50 pF

Internal Reference Buffer Output Current Limit Reference buffer boost mode disabled 3.5 mA

Reference buffer boost mode enabled 11 mA

Internal Reference Buffer Turn-On Time7 (tREFBUF) VREF = 5 V

Reference Buffer Boost Mode Disabled REF decoupling capacitor (CREF = 1 µF) 10 ms

CREF = 10 µF 80 ms

Reference Buffer Boost Mode Enabled CREF = 1 µF 1.2 ms

CREF = 10 µF 10 ms

TEMPERATURE SENSOR

Temperature Sensor Voltage TA = 25°C 680 mV

TA = 0°C 725 mV

Temperature Sensitivity TA = −40°C to +125°C −1.8 mV/°C

OVERVOLTAGE CLAMP

External Series Resistance (R 8

EXT) For stable clamp operation

Overvoltage reduced current mode disabled 2000 Ω

Overvoltage reduced current mode enabled 1000 Ω

External Series Capacitance (C )8

EXT For stable clamp operation 500 pF

Clamp Input Current For each active clamp 5 mA

Clamp Activation Voltage VREF + 0.55 V

Clamp Deactivation Voltage VREF + 0.1 V

Input Clamping Voltage Clamp current = 5 mA VREF + 0.2 V

Activation Time 50 ns

Deactivation Time 100 ns

DIGITAL INPUTS

Logic Levels

Input Low Voltage (VIL) −0.3 +0.3 × VIO V

Input High Voltage (VIH) 0.7 × VIO 3.6 V

Input Current (IL) −1 +1 µA

Input Pin Capacitance 5 pF

analog.com Rev. A | 8 of 107

Page9

Data Sheet AD4695/AD4696

SPECIFICATIONS

Table 1.

Parameter Test Conditions/Comments Min Typ Max Unit

DIGITAL OUTPUTS

Conversion Mode Data Format Unipolar mode Straight binary

Pseudobipolar mode Twos complement

Logic Levels

Output Low Voltage (VOL) Digital output current = +500 µA 0.4 V

Output High Voltage (VOH) Digital output current = −500 µA VIO − 0.3 V

POWER REQUIREMENTS

AVDD to AGND 3.15 5.5 V

LDO_IN to AGND Internal LDO enabled 2.4 5.5 V

Internal LDO disabled 0 V

VDD to AGND Internal LDO disabled 1.71 1.8 1.89 V

VIO to IOGND 1.14 1.98 V

POWER SUPPLY CURRENT9

Standby Current

AVDD AVDD = 5 V

Internal reference buffer disabled 160 nA

Internal reference buffer enabled 460 µA

LDO_IN LDO_IN = 5 V

Internal LDO enabled 9 µA

Internal LDO disabled 0.3 µA

VDD VDD = 1.8 V, internal LDO disabled

Internal reference buffer disabled 1.5 µA

Internal reference buffer enabled 5 µA

VIO VIO = 1.8 V 250 nA

AVDD Current (Conversion Mode) AVDD = 5 V

Internal Reference Buffer Disabled, Reference fS = 10 kSPS 680 nA

High-Z Mode Disabled, Analog Input High-Z Mode

Disabled

fS = 500 kSPS 26 µA

fS = 1 MSPS 52 µA

Internal Reference Buffer Disabled, Reference fS = 10 kSPS 13 µA

High-Z Mode Enabled, Analog Input High-Z Mode

Enabled

fS = 500 kSPS 0.64 0.73 mA

fS = 1 MSPS 1.28 1.46 mA

Internal Reference Buffer Enabled, Reference fS = 10 kSPS, REFIN = 4.096 V 450 µA

High-Z Mode Enabled, Analog Input High-Z Mode

Enabled

fS = 500 kSPS, REFIN = 4.096 V 1 1.14 mA

fS = 1 MSPS, REFIN = 4.096 V 1.5 1.78 mA

LDO_IN Current (Conversion Mode) LDO_IN = 5 V, internal LDO enabled

Reference High-Z Mode Disabled, Analog Input fS = 10 kSPS 52 µA

High-Z Mode Disabled

fS = 500 kSPS 2 mA

fS = 1 MSPS 4 mA

Reference High-Z Mode Enabled, Analog Input fS = 10 kSPS 64 µA

High-Z Mode Enabled

fS = 500 kSPS 2.6 3.3 mA

fS = 1 MSPS 5.2 6.6 mA

analog.com Rev. A | 9 of 107

Page10

Data Sheet AD4695/AD4696

SPECIFICATIONS

Table 1.

Parameter Test Conditions/Comments Min Typ Max Unit

VDD Current (Conversion Mode) VDD = 1.8 V, internal LDO disabled

Reference High-Z Mode Disabled, Analog Input fS = 10 kSPS 42 µA

High-Z Mode Disabled

fS = 500 kSPS 2 mA

fS = 1 MSPS 4 mA

Reference High-Z Mode Enabled, Analog Input fS = 10 kSPS 53 µA

High-Z Mode Enabled

fS = 500 kSPS 2.5 3.2 mA

fS = 1 MSPS 5 6.4 mA

VIO Dynamic Current VIO = 1.8 V

Register Configuration Mode Streaming mode, SCK frequency (fSCK) = 50 MHz 125 µA

Conversion Mode Status bits enabled

fS = 10 kSPS 3.5 µA

fS = 500 kSPS 162 µA

fS = 1 MSPS 325 360 µA

POWER DISSIPATION9 AVDD = 5 V, VIO = 1.8 V

Standby Power Dissipation

Internal LDO Disabled VDD = 1.8 V, internal reference buffer disabled 4 µW

VDD = 1.8 V, internal reference buffer enabled 2.3 mW

Internal LDO Enabled LDO_IN = 5 V, internal reference buffer disabled 46 µW

LDO_IN = 5 V, internal reference buffer enabled 2.3 mW

Power Dissipation, Internal LDO Disabled LDO_IN = AGND, VDD = 1.8 V

Internal Reference Buffer Disabled, Reference fS = 10 kSPS 85 µW

High-Z Mode Disabled, Analog Input High-Z Mode

Disabled

fS = 500 kSPS 4 mW

fS = 1 MSPS 8 mW

Internal Reference Buffer Disabled, Reference fS = 10 kSPS 170 µW

High-Z Mode Enabled, Analog Input High-Z Mode

Enabled

fS = 500 kSPS 8 9.8 mW

fS = 1 MSPS 16 19.5 mW

Internal Reference Buffer Enabled, Reference fS = 10 kSPS, REFIN = 4.096 V 2.4 mW

High-Z Mode Enabled, Analog Input High-Z Mode

Enabled

fS = 500 kSPS, REFIN = 4.096 V 9.8 11.8 mW

fS = 1 MSPS, REFIN = 4.096 V 17.1 21.1 mW

Power Dissipation, Internal LDO Enabled LDO_IN = 5 V

Internal Reference Buffer Disabled, Reference fS = 10 kSPS 270 µW

High-Z Mode Disabled, Analog Input High-Z Mode

Disabled

fS = 500 kSPS 10.5 mW

fS = 1 MSPS 21 mW

Internal Reference Buffer Disabled, Reference fS = 10 kSPS 395 µW

High-Z Mode Enabled, Analog Input High-Z Mode

Enabled

fS = 500 kSPS 16.5 20.5 mW

fS = 1 MSPS 33 41.0 mW

Internal Reference Buffer Enabled, Reference fS = 10 kSPS, REFIN = 4.096 V 2.6 mW

High-Z Mode Enabled, Analog Input High-Z Mode

Enabled

analog.com Rev. A | 10 of 107

Page11

Timing Specifications

Data Sheet AD4695/AD4696

SPECIFICATIONS

Table 1.

Parameter Test Conditions/Comments Min Typ Max Unit

fS = 500 kSPS, REFIN = 4.096 V 18.3 22.5 mW

fS = 1 MSPS, REFIN = 4.096 V 34.1 42.6 mW

Autocycle Mode Power Dissipation LDO_IN = 5 V, internal LDO enabled, autocycle mode

enabled

AC_CYC = 0x0 2.3 mW

AC_CYC = 0x7 0.2 mW

TEMPERATURE RANGE

Specified Performance TMIN to TMAX −40 +125 °C

1 See the Channel Configuration Options section for a detailed description of unipolar mode, pseudobipolar mode, and the channel pin assignment options.

2 IN+ and IN− represent the analog inputs connected to the positive and negative inputs of the AD4695/AD4696 ADC core via the internal multiplexer (see the Multiplexer

section and Channel Configuration Options section).

3 The analog input leakage current specification refers to the input current of the analog input pins during periods when the ADC is not performing conversions and the

analog input voltage is already settled.

4 Offset error and gain error specifications are taken with the offset and gain correction registers set to the default values, which correspond to no offset or gain correction.

See the Offset and Gain Correction section for more information.

5 %FS is the percentage of the ADC full scale (see the Transfer Function section for a definition of full scale).

6 The REFIN pin and internal reference buffer are only available on the WLCSP models of the AD4695/AD4696. All specifications and conditions regarding REFIN or the

internal reference buffer are therefore only relevant for WLCSP models.

7 The reference buffer turn-on time specification refers to the amount of time between the reference buffer being enabled and the REF voltage settling to 0.01% accuracy

(see the Internal Reference Buffer section).

8 REXT and CEXT refer to the resistor and capacitor, respectively, that make up the recommended external RC filters at the analog inputs (see the External RC Filter section).

9 For the power supply current and power dissipation specifications where analog input high-Z mode is enabled, analog input high-Z mode is set to be enabled for all

channels. The power consumption scales with the percentage of conversions performed with analog input high-Z mode enabled.

TIMING SPECIFICATIONS

AVDD = 3.15 V to 5.5 V, LDO_IN = 2.4 V to 5.5 V with internal LDO enabled, LDO_IN = AGND with internal LDO disabled, VDD = 1.71 V to

1.89 V with internal LDO disabled, VIO = 1.14 V to 1.98 V, AGND = REFGND = IOGND = 0 V, reference voltage (VREF) = 2.4 V to 5.1 V, fS = 1

MSPS for the AD4696, fS = 500 kSPS for the AD4695, digital output load capacitance = 20 pF, autocycle mode disabled, no active overvoltage

protection clamps, and TA = −40°C to +125°C, unless otherwise noted.

Table 2.

Parameter1 Symbol Min Typ Max Unit

Conversion Time tCONVERT 380 415 ns

Acquisition Time tACQ

Two-Cycle Command Mode, Standard Sequencer, or Advanced Sequencer Enabled

fS = 1 MSPS 715 ns

fS = 500 kSPS 1715 ns

Single-Cycle Command Mode2 Enabled

CNV Period (Time Between Conversions) tCYC

fS = 1 MSPS, Autocycle Mode Disabled 1000 ns

fS = 500 kSPS, Autocycle Mode Disabled 2000 ns

Autocycle Mode Enabled

AC_CYC = 0x0 8.5 10 11.5 μs

AC_CYC = 0x1 17 20 23 μs

AC_CYC = 0x2 34 40 46 μs

AC_CYC = 0x3 68 80 92 μs

AC_CYC = 0x4 85 100 115 μs

analog.com Rev. A | 11 of 107

Page12

Data Sheet AD4695/AD4696

SPECIFICATIONS

Table 2.

Parameter1 Symbol Min Typ Max Unit

AC_CYC = 0x5 170 200 230 μs

AC_CYC = 0x6 340 400 460 μs

AC_CYC = 0x7 680 800 920 μs

CNV High Time tCNVH 10 ns

CNV Low Time tCNVL 80 ns

CS High Time tCSBH 5 ns

CS Low to Digital Interface Ready Delay tEN 15 ns

CS High to SDO High Impedance Delay tCSBDIS 15 ns

SCK Period tSCK

Register Configuration Mode 40 ns

Conversion Mode 12.5 ns

SCK Low Time tSCKL

Register Configuration Mode 16 ns

Conversion Mode 5 ns

SCK High Time tSCKH

Register Configuration Mode 16 ns

Conversion Mode 5 ns

SDI Data Setup Time Prior to SCK Rising Edge tSSDI 2 ns

SDI Data Hold Time After SCK Rising Edge tHSDI 2 ns

SCK Falling Edge to Data Remains Valid Delay tHSDO 1.5 ns

SCK Falling Edge to Data Valid Delay tDSDO 10.5 ns

Last SCK Edge to CNV Rising Edge Delay tSCKCNV 80 ns

Last SCK Rising Edge to CS Rising Edge Delay tSCKCSB 1 ns

CNV Rising Edge to Busy Indicator Rising Edge (Busy Indicator Enabled on General-Purpose Pin) tCNVBSY 20 ns

CNV Rising Edge to Alert Indicator Transition (Alert Indicator Enabled on General-Purpose Pin) tCNVALT 425 ns

Busy Indicator Low Time, Autocycle Mode Enabled (Busy Indicator Enabled on General-Purpose Pin) tACBSY

AC_CYC = 0x0 8 µs

AC_CYC = 0x1 16.5 µs

AC_CYC = 0x2 33.5 µs

AC_CYC = 0x3 67.5 µs

AC_CYC = 0x4 84.5 µs

AC_CYC = 0x5 169 µs

AC_CYC = 0x6 339 µs

AC_CYC = 0x7 679 µs

Register Configuration Mode Setup Time tREGCONFIG 20 ns

RESET Low Time tRESETL 10 ns

Hardware Reset Delay (VDD Always Supplied) tHWR_DELAY 310 µs

Software Reset Delay tSWR_DELAY 310 µs

VDD Power-On Reset Delay tPOR_VDD 2 ms

VIO Power-On Reset Delay (VDD Supplied Externally) tPOR_VIO1 1.3 ms

LDO_IN Power-On Reset Delay tPOR_LDO 3.2 ms

VIO Power-On Reset Delay (VDD Supplied by Internal LDO) tPOR_VIO2 3 ms

LDO Wake-Up Command Power-On Reset Delay tWAKEUP_SW 3 ms

Hardware Reset Delay (Internal LDO Disabled) tWAKEUP_HW 3 ms

1 For all specifications, the relative voltages for the AVDD and REF inputs follow the operating conditions specified in the reference and power requirements sections of Table

1.

2 The acquisition time for single-cycle command mode depends on the sample rate and SCK frequency (see the Single-Cycle Command Mode section).

analog.com Rev. A | 12 of 107

Page13

Absolute Maximum Ratings、Thermal Resistance、Electrostatic Discharge (ESD) Ratings、ESD Ratings for AD4695/AD4696、ESD Caution

Data Sheet AD4695/AD4696

ABSOLUTE MAXIMUM RATINGS

Table 3.

Parameter Rating Table 4. Thermal Resistance

Analog Inputs Package Type θJA1 θJC2 Unit

INn,1 COM to REFGND −0.3 V to REF + 0.3 V CP-32-7 40.2 17.5 °C/W

Reference Inputs CP-36-5 41.8 0.1 °C/W

REF, REFIN to AGND, REFGND, IOGND −0.3 V to +6 V

REF to REFIN −6.3 V to +6.3 V 1 Simulated values are based on the JEDEC 2S2P thermal test board with

Supply Inputs nine thermal vias in a JEDEC natural convection environment. See JEDEC

AVDD, LDO_IN to AGND, REFGND, IOGND −0.3 V to +6 V JESD51.

VDD, VIO to AGND, REFGND, IOGND −0.3 V to +2.1 V 2 Simulated values are measured to the package top surface with a cold plate

AVDD to LDO_IN −6.3 V to +6.3 V attached directly to the package top surface.

AVDD, LDO_IN to REF −6.3 V to +6.3 V

VDD, VIO to AVDD, LDO_IN, REF −6.3 V to +2.4 V ELECTROSTATIC DISCHARGE (ESD) RATINGS

VDD to VIO −2.4 V to +2.4 V The following ESD information is provided for handling of ESD-sen-

Ground sitive devices in an ESD protected area only.

AGND, IOGND to REFGND −0.3 V to +0.3 V

AGND to IOGND −0.3 V to +0.3 V Human body model (HBM) per ANSI/ESDA/JEDEC JS-001.

Digital Inputs2 to IOGND −0.3 V to +6 V Field induced charged device model (FICDM) per ANSI/ESDA/JE-

Digital Outputs2 to IOGND −0.3 V to VIO + 0.3 V DEC JS-002.

Storage Temperature Range −65°C to +150°C

Junction Temperature 150°C ESD Ratings for AD4695/AD4696

Lead Temperature Soldering 260°C reflow, as per Table 5. AD4695/AD4696 32-Lead LFCSP

JEDEC J-STD-020 ESD Model Withstand Threshold (kV) Class

1 INn refers to the analog inputs, Pin IN0 through Pin IN15. HBM 4 3A

2 See the Pin Configuration and Function Descriptions section for a list of the FICDM 1.25 C3

digital input and digital output pins.

Table 6. AD4695/AD4696 36-Lead WLCSP

Stresses at or above those listed under Absolute Maximum Ratings ESD Model Withstand Threshold (kV) Class

may cause permanent damage to the product. This is a stress HBM 3 2

rating only; functional operation of the product at these or any other FICDM 1 C3

conditions above those indicated in the operational section of this

specification is not implied. Operation beyond the maximum operat- ESD CAUTION

ing conditions for extended periods may affect product reliability. ESD (electrostatic discharge) sensitive device. Charged devi-

THERMAL RESISTANCE ces and circuit boards can discharge without detection. Although

this product features patented or proprietary protection circuitry,

Thermal performance is directly linked to printed circuit board damage may occur on devices subjected to high energy ESD.

(PCB) design and operating environment. Careful attention to PCB Therefore, proper ESD precautions should be taken to avoid

thermal design is required. performance degradation or loss of functionality.

θJA is specified for worst case conditions and is the natural con-

vection junction-to-ambient thermal resistance measured in a one

cubic foot sealed enclosure, and θJC is the junction to case thermal

resistance.

Thermal resistance values specified in Table 4 were calculated

based on JEDEC specifications and must be used in compliance

with JESD51-12. The worst case junction temperature is reported.

θJA is highly dependent on the application and board layout. In

applications where high maximum power dissipation exists, close

attention to thermal board design is required. The θJA value can

vary depending on printed circuit board (PCB) material, layout, and

environmental conditions.

analog.com Rev. A | 13 of 107

Page14

Pin Configuration and Function Descriptions

Data Sheet AD4695/AD4696

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. AD4695/AD4696 LFCSP Pin Configuration

Table 7. AD4695/AD4696 LFCSP Pin Function Descriptions

Pin No. Mnemonic Type1 Description

1 IN5 AI Analog Input 5.

2 IN6 AI Analog Input 6.

3 IN7 AI Analog Input 7.

4 COM AI Common Channel Input. IN0 to IN15 can be paired with COM for the ADC core to sample the differential voltage between them.

COM is nominally tied to signal ground (unipolar mode) or VREF/2 (pseudobipolar mode). See the Channel Configuration Options

section for a detailed description on pairing inputs, unipolar mode, and pseudobipolar mode.

5 IN8 AI Analog Input 8.

6 IN9 AI Analog Input 9.

7 IN10 AI Analog Input 10.

8 IN11 AI Analog Input 11.

9 IN12 AI Analog Input 12.

10 IN13 AI Analog Input 13.

11 IN14 AI Analog Input 14.

12 IN15 AI Analog Input 15.

13 AGND P Analog Supply Ground. AVDD, LDO_IN, and VDD are referenced to AGND.

14 AVDD P Analog Power Supply. AVDD is nominally 3.15 V to 5.5 V. Decouple AVDD to AGND with a local 100 nF capacitor.

15 LDO_IN P Internal LDO Input. LDO_IN is nominally 2.4 V to 5.5 V when the internal LDO is enabled. Decouple LDO_IN to AGND with a

local 100 nF capacitor. If powering VDD with an external 1.8 V rail, tie LDO_IN to AGND. See the Internal LDO section for more

information.

16 VDD P ADC Core Power Supply. VDD is nominally 1.8 V. VDD must be decoupled with a local 100 nF capacitor to AGND. When the internal

LDO is enabled, VDD is internally generated. Disable the internal LDO when supplying VDD from an external source.

17 RESET DI Hardware Reset Input. Drive RESET low to perform a hardware reset of the device and reset the register states to the default values

(see the Device Reset section).

18 VIO P Input/Output Interface Digital Power. VIO is nominally the same supply as the host interface (for example, 1.2 V to 1.8 V). Decouple

VIO to IOGND with a local 100 nF capacitor.

19 IOGND P Input/Output Interface Digital Supply Ground. VIO is referenced to IOGND.

20 BSY_ALT_GP0 DI/DO General-Purpose Pin 0. On the LFCSP option, BSY_ALT_GP0 can be configured to function as a general-purpose input/output

(GPIO), the threshold detection alert indicator, the busy indicator, or the second serial data output in dual-SDO mode (see the

General-Purpose Pins section).

21 SDO DO Serial Data Output. When the device is configured in register configuration mode, SDO is used to read the configuration register data

during SPI read transactions. When the device is configured in conversion mode, SDO is used to read the conversion results. Data

output is synchronized to the falling edge of SCK.

22 SCK DI Serial Data Clock Input. SCK is used to clock out data on SDO and clock in data on SDI while the device is configured in either

register configuration mode or conversion mode.

23 SDI DI Serial Data Input. When the device is configured in register configuration mode, SDI is used to perform SPI read and write

transactions to access the configuration registers. In conversion mode, SDI receives 5-bit commands from the digital host, as shown

in Table 18.

analog.com Rev. A | 14 of 107

Page15

Data Sheet AD4695/AD4696

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Table 7. AD4695/AD4696 LFCSP Pin Function Descriptions

Pin No. Mnemonic Type1 Description

24 CNV DI Convert Input. When the device is configured in conversion mode, a rising edge on CNV initiates a conversion of the selected analog

input. The AD4695/AD4696 can interface to a 4-wire SPI by tying CNV to CS. See the Digital Interface Operation section for more

information.

25 CS DI Chip Select Input. When configured in register configuration mode, the CS pin frames the SPI read and write transactions that

access the configuration registers. When the device is configured in conversion mode, CS can either be held low throughout the

entire conversion or used to frame SPI transactions that read back conversion results. The AD4695/AD4696 can interface to a 4-wire

SPI by tying CNV to CS. See the Digital Interface Operation section for more information.

26 REFGND P Reference Ground. REF is referenced to REFGND. IN0 to IN15 can be paired with REFGND to the ADC core to sample the

differential voltage between them. See the Channel Configuration Options section for a detailed description on pairing inputs.

27 REF AI Reference Input. VREF must be provided by an external precision reference voltage between 2.4 V and 5.1 V. The REF pin must be

decoupled with a minimum 1 μF capacitor for optimal operation. See the Voltage Reference Input section for more information.

28 IN0 AI Analog Input 0.

29 IN1 AI Analog Input 1.

30 IN2 AI Analog Input 2.

31 IN3 AI Analog Input 3.

32 IN4 AI Analog Input 4.

33 EPAD NC Exposed Pad. The exposed pad is not connected internally. For increased reliability of the solder joints, it is recommended that the

pad be soldered to the system ground plane.

1 AI is analog input, P is power, DI is digital input, DO is digital output, and NC is no internal connection.

Figure 3. AD4695/AD4696 WLCSP Pin Configuration

Table 8. AD4695/AD4696 WLCSP Pin Function Descriptions

Pin No. Mnemonic Type1 Description

A1 SDI DI Serial Data Input. When the device is configured in register configuration mode, SDI is used to perform SPI read and write

transactions to access the configuration registers. In conversion mode, SDI receives 5-bit commands from the digital host, as

shown in Table 18.

A2 CS DI Chip Select Input. When configured in register configuration mode, the CS pin frames the SPI read and write transactions that

access the configuration registers. When the device is configured in conversion mode, CS can either be held low throughout

the entire conversion or used to frame SPI transactions that read back conversion results. The AD4695/AD4696 can interface

to a 4-wire SPI by tying CNV to CS. See the Digital Interface Operation section for more information.

A3 REFIN AI Internal Reference Buffer Input. The internal reference buffer can be used to buffer the reference voltage source and drive the

REF pin internally. When the internal reference buffer is enabled, REFIN must be driven by an external precision reference

source between 2.4 V and 5.1 V. When not using the internal reference buffer, REFIN must be tied to REF. See the Internal

Reference Buffer section for more information.

A4 IN0 AI Analog Input 0.

A5 IN2 AI Analog Input 2.

A6 IN3 AI Analog Input 3.

B1 SDO DO Serial Data Output. When the device is configured in register configuration mode, SDO is used to read the configuration

register data during SPI read transactions. When the device is configured in conversion mode, SDO is used to read the

conversion results. Data output is synchronized to the falling edge of SCK.

analog.com Rev. A | 15 of 107

Page16

Data Sheet AD4695/AD4696

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Table 8. AD4695/AD4696 WLCSP Pin Function Descriptions

Pin No. Mnemonic Type1 Description

B2 CNV DI Convert Input. When the device is configured in conversion mode, a rising edge on CNV initiates a conversion of the selected

analog input. The AD4695/AD4696 can interface to a 4-wire SPI by tying CNV to CS. See the Digital Interface Operation

section for more information.

B3 REF AI Reference Input. VREF must be provided by an external precision reference voltage between 2.4 V and 5.1 V. The REF pin

must be decoupled with a minimum 1 μF capacitor for optimal operation. See the Voltage Reference Input section for more

information.

B4 IN1 AI Analog Input 1.

B5 IN4 AI Analog Input 4.

B6 IN5 AI Analog Input 5.

C1 GP2 DI/DO General-Purpose Pin 2. Can be configured to function as a general-purpose input/output, the threshold detection alert indicator,

or the third serial data output in quad-SDO mode (see the General-Purpose Pins section).

C2 SCK DI Serial Data Clock Input. SCK is used to clock out data on SDO and clock in data on SDI while the device is configured in either

register configuration mode or conversion mode.

C3 REFGND P Reference Ground. REF is referenced to REFGND. IN0 to IN15 can be paired with REFGND to the ADC core to sample the

differential voltage between them. See the Channel Configuration Options section for a detailed description on pairing inputs.

C4 COM AI Common Channel Input. IN0 to IN15 can be paired with COM for the ADC core to sample the differential voltage between

them. COM is nominally tied to signal ground (unipolar mode) or VREF/2 (pseudobipolar mode). See the Channel Configuration

Options section for a detailed description on pairing inputs, unipolar mode, and pseudobipolar mode.

C5 IN6 AI Analog Input 6.

C6 IN7 AI Analog Input 7.

D1 BSY_ALT_GP0 DI/DO General-Purpose Pin 0. On the WLCSP option, BSY_ALT_GP0 can be configured to function as a general-purpose input/output

(GPIO), the threshold detection alert indicator, or the busy indicator (see the General-Purpose Pins section).

D2 GP1 DI/DO General-Purpose Pin 1. Can be configured to function as a general-purpose input/output, or the second serial data output in

dual- and quad-SDO modes (see the General-Purpose Pins section).

D3 RESET DI Hardware Reset Input. Drive RESET low to perform a hardware reset of the device and reset the register states to the default

values (see the Device Reset section).

D4 AGND P Analog Supply Ground. AVDD, LDO_IN, and VDD are referenced to AGND.

D5 IN9 AI Analog Input 9.

D6 IN8 AI Analog Input 8.

E1 VIO P Input/Output Interface Digital Power. VIO is nominally the same supply as the host interface (for example, 1.2 V to 1.8 V).

Decouple VIO to IOGND with a local 100 nF capacitor.

E2 GP3 DI/DO General-Purpose Pin 3. Can be configured to function as a general-purpose input/output, the busy indicator, or the fourth serial

data output in quad-SDO mode (see the General-Purpose Pins section).

E3 IOGND P Input/Output Interface Digital Supply Ground. VIO is referenced to IOGND.

E4 IN14 AI Analog Input 14.

E5 IN11 AI Analog Input 11.

E6 IN10 AI Analog Input 10.

F1 VDD P ADC Core Power Supply. VDD is nominally 1.8 V. VDD must be decoupled with a local 100 nF capacitor to AGND. When the

internal LDO is enabled, VDD is internally generated. Disable the internal LDO when supplying VDD from an external source.

F2 LDO_IN P Internal LDO Input. LDO_IN is nominally 2.4 V to 5.5 V when the internal LDO is enabled. Decouple LDO_IN to AGND with a

local 100 nF capacitor. If powering VDD with an external 1.8 V rail, tie LDO_IN to AGND. See the Internal LDO section for more

information.

F3 AVDD P Analog Power Supply. AVDD is nominally 3.15 V to 5.5 V. Decouple AVDD to AGND with a local 100 nF capacitor.

F4 IN15 AI Analog Input 15.

F5 IN13 AI Analog Input 13.

F6 IN12 AI Analog Input 12.

1 AI is analog input, P is power, DI is digital input, DO is digital output, and NC is no internal connection.

analog.com Rev. A | 16 of 107

Page17

Typical Performance Characteristics

Data Sheet AD4695/AD4696

TYPICAL PERFORMANCE CHARACTERISTICS

AVDD = LDO_IN = 5 V, VIO = 1.8 V, VREF = 5 V, fSCK = 50 MHz, unipolar mode, analog input high-Z mode enabled, reference input high-Z

mode enabled, internal LDO enabled, fS = 1 MSPS for the AD4696, fS = 500 kSPS for the AD4695, no active clamps, autocycle mode disabled,

OSR = 1, and TA = 25°C, unless otherwise specified.

Figure 4. INL vs. Code, VREF = 5 V Figure 7. DNL vs. Code, VREF = 5 V

Figure 5. INL vs. Code, VREF = 4.096 V Figure 8. DNL vs. Code, VREF = 4.096 V

Figure 6. INL vs. Code, VREF = 2.5 V Figure 9. DNL vs. Code, VREF = 2.5 V

analog.com Rev. A | 17 of 107

Page18

Data Sheet AD4695/AD4696

TYPICAL PERFORMANCE CHARACTERISTICS

Figure 10. Histogram of a DC Input at Code Center, OSR = 1 Figure 13. Histogram of a DC Input at Code Transition, OSR = 1

Figure 11. Histogram of a DC Input at Code Center, OSR = 64 Figure 14. Histogram of a DC Input at Code Transition, OSR = 64

Figure 12. Dynamic Range vs. OSR Figure 15. 1/f Noise (0.1 Hz to 10 Hz Bandwidth), 50 kSPS, 2500 Samples

Averaged per Reading

analog.com Rev. A | 18 of 107

Page19

Data Sheet AD4695/AD4696

TYPICAL PERFORMANCE CHARACTERISTICS

Figure 16. Fast Fourier Transform (FFT), fIN = 1 kHz, VREF = 5 V, OSR = 1 Figure 19. FFT, fIN = 1 kHz, VREF = 2.5 V, OSR = 1

Figure 17. FFT, fIN = 1 kHz, VREF = 5 V, OSR = 64 Figure 20. FFT, fIN = 1 kHz, VREF = 2.5 V, OSR = 64

Figure 18. SNR, SINAD, and THD vs. Input Frequency

Figure 21. Analog Input Voltage Step with Analog Input High-Z Mode

Disabled and Enabled

analog.com Rev. A | 19 of 107

Page20

Data Sheet AD4695/AD4696

TYPICAL PERFORMANCE CHARACTERISTICS

Figure 22. SNR, SINAD, and Effective Number of Bits (ENOB) vs. VREF, fIN = 1 Figure 25. THD and SFDR vs. VREF, fIN = 1 kHz

kHz

Figure 26. THD and SFDR vs. Temperature, fIN = 1 kHz

Figure 23. SNR, SINAD, and ENOB vs. Temperature, fIN = 1 kHz

Figure 27. SNR, SINAD vs. Number of Active Clamps, Reduced Current Mode

Figure 24. SNR, SINAD vs. Number of Active Clamps, Reduced Current Mode Enabled

Disabled

analog.com Rev. A | 20 of 107