1/63ページ

ダウンロード(552.9Kb)

High-Reliability, Tiny, Ultra-Low-Power Arm Cortex-M4F Microcontroller with 12-Bit, 1Msps ADC

このカタログについて

| ドキュメント名 | MAX32672 Ultra-Low-Power Arm |

|---|---|

| ドキュメント種別 | 製品カタログ |

| ファイルサイズ | 552.9Kb |

| 取り扱い企業 | マウザー・エレクトロニクス (この企業の取り扱いカタログ一覧) |

この企業の関連カタログ

このカタログの内容

Page1

General Description、Applications、Benefits and Features

Click here to ask an associate for production status of specific part numbers.

MAX32672 High-Reliability, Tiny, Ultra-Low-Power

Arm Cortex-M4F Microcontroller

with 12-Bit, 1Msps ADC

General Description Benefits and Features

In the DARWIN family, the MAX32672 is an ultra-low- ● High-Efficiency Microcontroller for Low-Power High-

power, cost-effective, highly integrated, and highly reliable Reliability Devices

32-bit microcontroller enabling designs with complex sen- • Arm Cortex-M4 Processor with FPU up to 100MHz

sor processing without compromising battery life. It com- • 1MB Dual-Bank Flash with Error Correction

bines a flexible and versatile power management unit with • 200KB SRAM (160KB with ECC Enabled),

the powerful Arm® Cortex®-M4 processor with a floating- Optionally Preserved in Lowest Power Modes

point unit (FPU). The MAX32672 also offers legacy de- • EEPROM Emulation on Flash

signs an easy and cost-optimal upgrade path from 8- or • 16KB Unified Cache with ECC

16-bit microcontrollers. • Resource Protection Unit (RPU) and Memory

The device integrates 1MB of flash and 200KB of SRAM Protection Unit (MPU)

to accommodate application and sensor code. Error cor- • Dual- or Single-Supply Operation, 1.7V to 3.6V

rection coding (ECC) is implemented on the entire flash, • Wide Operating Temperature: -40°C to +105°C

RAM, and cache to ensure extremely reliable code execu- ● Flexible Clocking Schemes

tion even in the harshest of environments. Brownout de- • Internal High-Speed 100MHz Oscillator

tection ensures proper operation during power-down and • Internal Low-Power 7.3728MHz and Ultra-Low-

power-up events and unexpected supply transients. The Power 80kHz Oscillators

flash is organized into two equal-size physical banks to al- • 16MHz–32MHz Oscillator, 32.768kHz Oscillator

low execute-while-write and facilitate "live upgrades." (External Crystal Required)

Multiple high-speed peripherals such as 3.4MHz I2C, • External Clock Input for CPU, LPUART, LPTIMER

50MHz SPI, and UART are included to maximize com- ● Power Management Maximizes Uptime for Battery

munication bandwidth. In addition, a low-power UART Applications

(LPUART) is available for operation in the lowest power • 53.2μA/MHz ACTIVE at 0.9V up to 12MHz

sleep modes to facilitate wake-up activity without any loss (CoreMark®)

of data. A total of six timers with I/O capability are provid- • 61.5μA/MHz ACTIVE at 1.1V up to 100MHz

ed, including two low-power timers to enable pulse count- • 2.94μA Full Memory Retention Power in BACKUP

ing, capture/compare, and pulse-width modulation (PWM) Mode at VDD = 1.8V

generation, even in the lowest power sleep modes. An in- • 350nA Ultra-Low-Power RTC at VDD = 1.8V

cremental/quadrature encoder interface with multiple diag- • Wake from LPUART or LPTMR

nostics is included specifically for motor control applica- ● Optimal Peripheral Mix Provides Platform Scalability

tions. A 1Msps, 12-channel, 12-bit successive approxima- • Up to 42 General-Purpose I/O Pins

tion register (SAR) ADC is integrated for the digitization • Up to Three SPI Master/Slave (up to 50Mbps)

of analog sensor signals or other analog measurements. • Up to Three 4-Wire UART

Two low-power comparators, available in all low-power • Up to Three I2C Master/Slave 3.4Mbps High Speed

modes, allow energy-efficient monitoring and wake-up on • Up to Four 32-Bit Timers (TMR)

external analog signals. An Elliptic Curve Digital Signa- • Up to Two Low-Power 32-Bit Timers (LPTMR)

ture Algorithm (ECDSA)-based cryptographic secure boot- • One I2S Master/Slave for Digital Audio Interface

loader is available in ROM. The device is available in a • One 12-Channel, 12-Bit, 1Msps SAR ADC with On-

5mm x 5mm, 40-pin TQFN-EP or 7mm x 7mm, 56-pin Die Temperature Sensor

TQFN.

● Security and Integrity

Applications • Available ECDSA-Based Cryptographic Secure

Bootloader in ROM

● Motion/Motor Control, Industrial Sensors • Secure Loader Interface over UART

● Optical Communication Modules, Secure Radio • AES-128/192/256 Hardware Acceleration Engine

Modem Controller • TRNG Compliant to SP800-90B

● Battery-Powered Medical Devices

Arm and Cortex are registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere.

CoreMark is a registered trademark of EEMBC.

Ordering Information appears at end of data sheet. 19-101210; Rev 1; 1/22

© 2022 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners.

One Analog Way, Wilmington, MA 01887 U.S.A. | Tel: 781.329.4700 | © 2022 Analog Devices, Inc. All rights reserved.

Page2

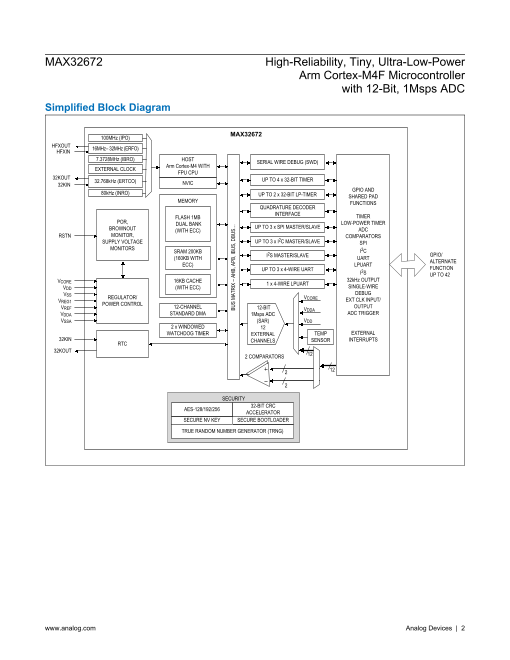

Simplified Block Diagram

MAX32672 High-Reliability, Tiny, Ultra-Low-Power

Arm Cortex-M4F Microcontroller

with 12-Bit, 1Msps ADC

Simplified Block Diagram

100MHz (IPO) MAX32672

HFXOUT

HFXIN 16MHz– 32MHz (ERFO)

7.3728MHz (IBRO) HOST SERIAL WIRE DEBUG (SWD)

EXTERNAL CLOCK Arm Cortex-M4 WITH

FPU CPU

32KOUT

32KIN 32.768kHz (ERTCO) NVIC UP TO 4 x 32-BIT TIMER

80kHz (INRO) GPIO AND

UP TO 2 x 32-BIT LP-TIMER SHARED PAD

MEMORY FUNCTIONS

QUADRATURE DECODER

FLASH 1MB INTERFACE TIMER

POR, DUAL BANK LOW-POWER TIMER

BROWNOUT (WITH ECC) UP TO 3 x SPI MASTER/SLAVE ADC

RSTN MONITOR, COMPARATORS

SUPPLY VOLTAGE UP TO 3 x I2C MASTER/SLAVE SPI

MONITORS SRAM 200KB 2

2 I C

(160KB WITH I S MASTER/SLAVE UART GPIO/

ECC) LPUART ALTERNATE

UP TO 3 x 4-WIRE UART 2 FUNCTION

I S UP TO 42

VCORE 16KB CACHE 32kHz OUTPUT

(WITH ECC) 1 x 4-WIRE LPUART

VDD SINGLE-WIRE

VSS DEBUG

V REGULATOR/ VCORE

REG1 EXT CLK INPUT/

V POWER CONTROL

REF 12-CHANNEL 12-BIT V OUTPUT

VDDA STANDARD DMA DDA

1Msps ADC ADC TRIGGER

VSSA (SAR) VDD

2 x WINDOWED 12

WATCHDOG TIMER EXTERNAL TEMP EXTERNAL

32KIN

RTC CHANNELS SENSOR INTERRUPTS

32KOUT

2 COMPARATORS 12

2 12

2

SECURITY

AES-128/192/256 32-BIT CRC

ACCELERATOR

SECURE NV KEY SECURE BOOTLOADER

TRUE RANDOM NUMBER GENERATOR (TRNG)

www.analog.com Analog Devices | 2

BUS MATRIX – AHB, APB, IBUS, DBUS…

Page3

MAX32672 High-Reliability, Tiny, Ultra-Low-Power

Arm Cortex-M4F Microcontroller

with 12-Bit, 1Msps ADC

TABLE OF CONTENTS

General Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Benefits and Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Simplified Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Package Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

40 TQFN-EP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

56 TQFN-EP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8

Electrical Characteristics—SPI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

Electrical Characteristics—I2C . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

Electrical Characteristics—I2S Slave . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Electrical Characteristics—Quadrature Decoder . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 38

Pin Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

40 TQFN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

Pin Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

56 TQFN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Detailed Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Arm Cortex-M4 Processor with FPU Engine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Internal Flash Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Internal SRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Clocking Scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

General-Purpose I/O and Special Function Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Standard DMA Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Power Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

Power Management Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

ACTIVE Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

SLEEP Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

DEEPSLEEP Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

BACKUP Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

STORAGE Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Real-Time Clock (RTC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Windowed Watchdog Timer (WDT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

32-Bit Timer/Counter/PWM (TMR, LPTMR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Serial Peripherals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

I2C Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

www.analog.com Analog Devices | 3

Page4

MAX32672 High-Reliability, Tiny, Ultra-Low-Power

Arm Cortex-M4F Microcontroller

with 12-Bit, 1Msps ADC

TABLE OF CONTENTS (CONTINUED)

Serial Peripheral Interface (SPI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

I2S Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

UART . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Quadrature Decoder . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Analog-to-Digital Converter (ADC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Security . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

AES . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

True Random Number Generator (TRNG) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

CRC Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Root of Trust . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Secure Communications Protocol Bootloader (SCPBL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Secure Boot . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Debug and Development Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

Applications Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Bypass Capacitors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Bootloader Activation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

www.analog.com Analog Devices | 4

Page5

MAX32672 High-Reliability, Tiny, Ultra-Low-Power

Arm Cortex-M4F Microcontroller

with 12-Bit, 1Msps ADC

LIST OF FIGURES

Figure 1. Power Supply Operational Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

Figure 2. SPI Master Mode Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Figure 3. SPI Slave Mode Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Figure 4. I2C Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Figure 5. I2S Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Figure 6. Quadrature Decoder Timing Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 42

Figure 7. Clocking Scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

www.analog.com Analog Devices | 5

Page6

MAX32672 High-Reliability, Tiny, Ultra-Low-Power

Arm Cortex-M4F Microcontroller

with 12-Bit, 1Msps ADC

LIST OF TABLES

Table 1. BACKUP Mode RAM Retention . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

Table 2. Timer Configuration Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Table 3. SPI Configuration Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 58

Table 4. UART Configuration Options . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 59

Table 5. Bootloader Activation Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 62

www.analog.com Analog Devices | 6

Page7

Absolute Maximum Ratings、Package Information、40 TQFN-EP、56 TQFN-EP

MAX32672 High-Reliability, Tiny, Ultra-Low-Power

Arm Cortex-M4F Microcontroller

with 12-Bit, 1Msps ADC

Absolute Maximum Ratings

VCORE, HFXIN, HFXOUT ................................... -0.3V to +1.21V Continuous Package Power Dissipation 40 TQFN-EP (multilayer

VDD, VDDA .......................................................... -0.3V to +3.63V board) TA = +70°C (derate 35.7mW/°C above

VREF ........................................................... -0.3V to VDDA + 0.3V +70°C) ........................................................................2857.10mW

32KIN, 32KOUT ........................................... -0.3V to VDD + 0.3V Continuous Package Power Dissipation 56 TQFN-EP (multilayer

RSTN, GPIO ................................................. -0.3V to VDD + 0.3V board) TA = +70°C (derate 40mW/°C above +70°C) ......3200mW

Total Current into All GPIO Combined (sink) .................... 100mA Operating Temperature Range ...........................-40°C to +105°C

VSS .................................................................................... 100mA Storage Temperature Range ..............................-65°C to +150°C

Output Current (sink) by Any GPIO Pin ............................... 25mA Soldering Temperature (reflow) ........................................+260°C

Output Current (source) by Any GPIO Pin ......................... -25mA

Note: No device pins can exceed 3.63V. All voltages with respect to VSS, unless otherwise noted.

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the

device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for

extended periods may affect device reliability.

Package Information

40 TQFN-EP

Package Code T4055+1

Outline Number 21-0140

Land Pattern Number 90-0016

Thermal Resistance, Single-Layer Board:

Junction to Ambient (θJA) 45°C/W

Junction to Case (θJC) 2°C/W

Thermal Resistance, Four-Layer Board:

Junction to Ambient (θJA) 28°C/W

Junction to Case (θJC) 2°C/W

56 TQFN-EP

Package Code T5677+1

Outline Number 21-0144

Land Pattern Number 90-0042

Thermal Resistance, Single-Layer Board:

Junction to Ambient (θJA) 36°C/W

Junction to Case (θJC) 1°C/W

Thermal Resistance, Four-Layer Board:

Junction to Ambient (θJA) 25°C/W

Junction to Case (θJC) 1°C/W

For the latest package outline information and land patterns (footprints), go to www.maximintegrated.com/packages. Note that a “+”, “#”, or “-” in the package code indicates

RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal

considerations, refer to www.maximintegrated.com/thermal-tutorial.

www.analog.com Analog Devices | 7

Page8

Electrical Characteristics

MAX32672 High-Reliability, Tiny, Ultra-Low-Power

Arm Cortex-M4F Microcontroller

with 12-Bit, 1Msps ADC

Electrical Characteristics

(Limits are 100% tested at TA = +25°C and TA = +105°C. Limits over the operating temperature range and relevant supply voltage

range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested.

Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

POWER / BOTH SINGLE-SUPPLY OPERATION AND DUAL-SUPPLY OPERATION

Supply Voltage VDD 1.71 1.8 3.63 V

OVR = [00] 0.855 0.9 0.945

Dual-supply

operation OVR = [01] 0.95 1.0 1.05 V

Supply Voltage, Core VCORE Default OVR = [10] 1.045 1.1 1.155

No power supply connection for single-

supply operation —

Supply Voltage, Analog VDDA VDDA must be connected to VDD 1.71 3.63 V

Monitors VDD 1.58 1.71

Power-Fail Reset

Voltage VRST Monitors VCORE during dual-supply V

operation 0.74 0.845

Monitors V 1.4

Power-On Reset DD

Voltage VPOR Monitors VCORE during dual-supply V

operation 0.6

www.analog.com Analog Devices | 8

Page9

Electrical Characteristics (continued)

MAX32672 High-Reliability, Tiny, Ultra-Low-Power

Arm Cortex-M4F Microcontroller

with 12-Bit, 1Msps ADC

Electrical Characteristics (continued)

(Limits are 100% tested at TA = +25°C and TA = +105°C. Limits over the operating temperature range and relevant supply voltage

range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested.

Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

POWER / SINGLE-SUPPLY OPERATION (VDD ONLY); fSYS_OSC = IPO

OVR = [10],

internal regulator

Dynamic, IPO set to 1.1V, 62.9

enabled, total fSYS_CLK(MAX) =

current into V 100MHz

DD

pin, VDD = 3.3V, OVR = [01],

CPU in ACTIVE internal regulator

mode, executing set to 1.0V, 64.9

CoreMark, ECC fSYS_CLK(MAX) =

disabled, inputs 50MHz

tied to VSS or VDD, OVR = [00],

outputs source/sink internal regulator

0mA set to 0.9V, 62.4

fSYS_CLK(MAX) =

12MHz

OVR = [10],

internal regulator

Dynamic, IPO set to 1.1V, 61.4

enabled, total fSYS_CLK(MAX) =

current into V 100MHz

DD

pin, VDD = 1.8V, OVR = [01],

V Current ACTIVE CPU in ACTIVE internal regulator

DD

Mode IDD_DACTS mode, executing set to 1.0V, 63 μA/MHz

CoreMark, ECC fSYS_CLK(MAX) =

disabled, inputs 50MHz

tied to VSS or VDD, OVR = [00],

outputs source/sink internal regulator

0mA set to 0.9V, 60.9

fSYS_CLK(MAX) =

12MHz

OVR = [10],

internal regulator

Dynamic, IPO set to 1.1V, 51.6

enabled, total fSYS_CLK(MAX) =

current into V 100MHz

DD

pin, VDD = 3.3V, OVR = [01],

CPU in ACTIVE internal regulator

mode, executing set to 1.0V, 52.1

While(1), ECC fSYS_CLK(MAX) =

disabled, inputs 50MHz

tied to VSS or VDD, OVR = [00],

outputs source/sink internal regulator

0mA set to 0.9V, 50.8

fSYS_CLK(MAX) =

12MHz

www.analog.com Analog Devices | 9

Page10

MAX32672 High-Reliability, Tiny, Ultra-Low-Power

Arm Cortex-M4F Microcontroller

with 12-Bit, 1Msps ADC

Electrical Characteristics (continued)

(Limits are 100% tested at TA = +25°C and TA = +105°C. Limits over the operating temperature range and relevant supply voltage

range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested.

Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

OVR = [10],

internal regulator

Dynamic, IPO set to 1.1V, 49.8

enabled, total fSYS_CLK(MAX) =

current into V 100MHz

DD

pin, VDD = 1.8V, OVR = [01],

CPU in ACTIVE internal regulator

mode, executing set to 1.0V, 50.4

While(1), ECC fSYS_CLK(MAX) =

disabled, inputs 50MHz

tied to VSS or VDD, OVR = [00],

outputs source/sink internal regulator

0mA set to 0.9V, 49.2

fSYS_CLK(MAX) =

12MHz

Fixed, IPO OVR = [10],

enabled, total internal regulator 900

current into VDD set to 1.1V

pin, VDD = 3.3V, OVR = [01],

CPU in ACTIVE internal regulator 751

mode 0MHz set to 1.0V

execution, ECC

disabled, inputs OVR = [00],

tied to VSS or VDD, internal regulator 618

outputs source/sink set to 0.9V

0mA

IDD_FACTS μA

Fixed, IPO OVR = [10],

enabled, total internal regulator 873

current into VDD set to 1.1V

pin, VDD = 1.8V, OVR = [01],

CPU in ACTIVE internal regulator 729

mode 0MHz set to 1.0V

execution, ECC

disabled, inputs OVR = [00],

tied to VSS or VDD, internal regulator 594

outputs source/sink set to 0.9V

0mA

www.analog.com Analog Devices | 10

Page11

MAX32672 High-Reliability, Tiny, Ultra-Low-Power

Arm Cortex-M4F Microcontroller

with 12-Bit, 1Msps ADC

Electrical Characteristics (continued)

(Limits are 100% tested at TA = +25°C and TA = +105°C. Limits over the operating temperature range and relevant supply voltage

range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested.

Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

OVR = [10],

internal regulator

Dynamic, IPO set to 1.1V, 36.6

enabled, total fSYS_CLK(MAX) =

current into VDD 100MHz

pin, VDD = 3.3V,

CPU in SLEEP OVR = [01],

mode, ECC internal regulator

disabled, standard set to 1.0V, 38.3

DMA with two fSYS_CLK(MAX) =

channels active, 50MHz

inputs tied to VSS OVR = [00],

or VDD, outputs internal regulator

source/sink 0mA set to 0.9V, 38.7

fSYS_CLK(MAX) =

12MHz

OVR = [10],

internal regulator

Dynamic, IPO set to 1.1V, 36.5

enabled, total fSYS_CLK(MAX) =

current into VDD 100MHz

pin, VDD = 1.8V,

CPU in SLEEP OVR = [01],

V Current SLEEP mode, ECC internal regulator

DD

Mode IDD_DSLPS disabled, standard set to 1.0V, 37.9 μA/MHz

DMA with two fSYS_CLK(MAX) =

channels active, 50MHz

inputs tied to VSS OVR = [00],

or VDD, outputs internal regulator

source/sink 0mA set to 0.9V, 38.7

fSYS_CLK(MAX) =

12MHz

OVR = [10],

internal regulator

Dynamic, IPO set to 1.1V, 12.5

enabled, total fSYS_CLK(MAX) =

current into V 100MHz

DD

pin, VDD = 3.3V, OVR = [01],

CPU in SLEEP internal regulator

mode, ECC set to 1.0V, 11.6

disabled, DMA fSYS_CLK(MAX) =

disabled, inputs 50MHz

tied to VSS or VDD, OVR = [00],

outputs source/sink internal regulator

0mA set to 0.9V, 12.9

fSYS_CLK(MAX) =

12MHz

www.analog.com Analog Devices | 11

Page12

MAX32672 High-Reliability, Tiny, Ultra-Low-Power

Arm Cortex-M4F Microcontroller

with 12-Bit, 1Msps ADC

Electrical Characteristics (continued)

(Limits are 100% tested at TA = +25°C and TA = +105°C. Limits over the operating temperature range and relevant supply voltage

range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested.

Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

OVR = [10],

internal regulator

Dynamic, IPO set to 1.1V, 12.7

enabled, total fSYS_CLK(MAX) =

current into V 100MHz

DD

pin, VDD = 1.8V, OVR = [01],

CPU in SLEEP internal regulator

mode, ECC set to 1.0V, 12

disabled, DMA fSYS_CLK(MAX) =

disabled, inputs 50MHz

tied to VSS or VDD, OVR = [00],

outputs source/sink internal regulator

0mA set to 0.9V, 14.9

fSYS_CLK(MAX) =

12MHz

Fixed, IPO OVR = [10],

enabled, total internal regulator 900

current into VDD set to 1.1V

pin, VDD = 3.3V, OVR = [01],

CPU in SLEEP internal regulator 751

mode, ECC set to 1.0V

disabled, inputs

tied to VSS or VDD, OVR = [00],

outputs source/sink internal regulator 618

0mA set to 0.9V

IDD_FSLPS μA

Fixed, IPO OVR = [10],

enabled, total internal regulator 873

current into VDD set to 1.1V

pin, VDD = 1.8V, OVR = [01],

CPU in SLEEP internal regulator 729

mode, ECC set to 1.0V

disabled, inputs

tied to VSS or VDD, OVR = [00],

outputs source/sink internal regulator 594

0mA set to 0.9V

SLEEP Mode Resume

Time tSLP_ONS fSYS_OSC = IPO 0.1 μs

DEEPSLEEP Mode fast_wk_en = 1 74

Resume Time tDSL_ONS fSYS_OSC = IPO μs

fast_wk_en = 0 210

BACKUP Mode Resume fSYS_OSC = IPO, includes system

Time tBKU_ONS initialization and ROM execution time 1.08 ms

STORAGE Mode t fSYS_OSC = IPO, includes system

Resume Time STO_ONS initialization and ROM execution time 1.08 ms

www.analog.com Analog Devices | 12

Page13

MAX32672 High-Reliability, Tiny, Ultra-Low-Power

Arm Cortex-M4F Microcontroller

with 12-Bit, 1Msps ADC

Electrical Characteristics (continued)

(Limits are 100% tested at TA = +25°C and TA = +105°C. Limits over the operating temperature range and relevant supply voltage

range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested.

Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

POWER / SINGLE-SUPPLY OPERATION (VDD ONLY); fSYS_OSC = IBRO

OVR = [10],

internal regulator

Dynamic, IBRO set to 1.1V, 78

enabled, total fSYS_CLK(MAX) =

current into V 7.3728MHz

DD

pin, VDD = 3.3V, OVR = [01],

CPU in ACTIVE internal regulator

mode, executing set to 1.0V, 78

CoreMark, ECC fSYS_CLK(MAX) =

disabled, inputs 7.3728MHz

tied to VSS or VDD, OVR = [00],

outputs source/sink internal regulator

0mA set to 0.9V, 71

fSYS_CLK(MAX) =

7.3728MHz

OVR = [10],

internal regulator

Dynamic, IBRO set to 1.1V, 74.6

enabled, total fSYS_CLK(MAX) =

current into V 7.3728MHz

DD

pin, VDD = 1.8V, OVR = [01],

V Current ACTIVE CPU in ACTIVE internal regulator

DD

Mode IDD_DACTS mode, executing set to 1.0V, 74.4 μA/MHz

CoreMark, ECC fSYS_CLK(MAX) =

disabled, inputs 7.3728MHz

tied to VSS or VDD, OVR = [00],

outputs source/sink internal regulator

0mA set to 0.9V, 67.6

fSYS_CLK(MAX) =

7.3728MHz

OVR = [10],

internal regulator

Dynamic, IBRO set to 1.1V, 67.5

enabled, total fSYS_CLK(MAX) =

current into V 7.3728MHz

DD

pin, VDD = 3.3V, OVR = [01],

CPU in ACTIVE internal regulator

mode, executing set to 1.0V, 66.7

While(1), ECC fSYS_CLK(MAX) =

disabled, inputs 7.3728MHz

tied to VSS or VDD, OVR = [00],

outputs source/sink internal regulator

0mA set to 0.9V, 60.6

fSYS_CLK(MAX) =

7.3728MHz

www.analog.com Analog Devices | 13

Page14

MAX32672 High-Reliability, Tiny, Ultra-Low-Power

Arm Cortex-M4F Microcontroller

with 12-Bit, 1Msps ADC

Electrical Characteristics (continued)

(Limits are 100% tested at TA = +25°C and TA = +105°C. Limits over the operating temperature range and relevant supply voltage

range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested.

Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

OVR = [10],

internal regulator

Dynamic, IBRO set to 1.1V, 63.7

enabled, total fSYS_CLK(MAX) =

current into V 7.3728MHz

DD

pin, VDD = 1.8V, OVR = [01],

CPU in ACTIVE internal regulator

mode, executing set to 1.0V, 62.4

While(1), ECC fSYS_CLK(MAX) =

disabled, inputs 7.3728MHz

tied to VSS or VDD, OVR = [00],

outputs source/sink internal regulator

0mA set to 0.9V, 57.1

fSYS_CLK(MAX) =

7.3728MHz

Fixed, IBRO OVR = [10],

enabled, total internal regulator 423

current into VDD set to 1.1V

pin, VDD = 3.3V, OVR = [01],

CPU in ACTIVE internal regulator 357

mode 0MHz set to 1.0V

execution, ECC

disabled, inputs OVR = [00],

tied to VSS or VDD, internal regulator 298

outputs source/sink set to 0.9V

0mA

IDD_FACTS μA

Fixed, IBRO OVR = [10],

enabled, total internal regulator 376

current into VDD set to 1.1V

pin, VDD = 1.8V, OVR = [01],

CPU in ACTIVE internal regulator 334

mode 0MHz set to 1.0V

execution, ECC

disabled, inputs OVR = [00],

tied to VSS or VDD, internal regulator 276

outputs source/sink set to 0.9V

0mA

www.analog.com Analog Devices | 14

Page15

MAX32672 High-Reliability, Tiny, Ultra-Low-Power

Arm Cortex-M4F Microcontroller

with 12-Bit, 1Msps ADC

Electrical Characteristics (continued)

(Limits are 100% tested at TA = +25°C and TA = +105°C. Limits over the operating temperature range and relevant supply voltage

range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested.

Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

OVR = [10],

internal regulator

Dynamic, IBRO set to 1.1V, 51.8

enabled, total fSYS_CLK(MAX) =

current into VDD 7.3728MHz

pin, VDD = 3.3V,

CPU in SLEEP OVR = [01],

mode, ECC internal regulator

disabled, standard set to 1.0V, 52

DMA with two fSYS_CLK(MAX) =

channels active, 7.3728MHz

inputs tied to VSS OVR = [00],

or VDD, outputs internal regulator

source/sink 0mA set to 0.9V, 48.2

fSYS_CLK(MAX) =

7.3728MHz

OVR = [10],

internal regulator

Dynamic, IBRO set to 1.1V, 51.4

enabled, total fSYS_CLK(MAX) =

current into VDD 7.3728MHz

pin, VDD = 1.8V,

CPU in SLEEP OVR = [01],

V Current SLEEP mode, ECC internal regulator

DD

Mode IDD_DSLPS disabled, standard set to 1.0V, 50.4 μA/MHz

DMA with two fSYS_CLK(MAX) =

channels active, 7.3728MHz

inputs tied to VSS OVR = [00],

or VDD, outputs internal regulator

source/sink 0mA set to 0.9V, 46.5

fSYS_CLK(MAX) =

7.3728MHz

OVR = [10],

internal regulator

Dynamic, IBRO set to 1.1V, 27.5

enabled, total fSYS_CLK(MAX) =

current into V 7.3728MHz

DD

pin, VDD = 3.3V, OVR = [01],

CPU in SLEEP internal regulator

mode, ECC set to 1.0V, 26

disabled, DMA fSYS_CLK(MAX) =

disabled, inputs 7.3728MHz

tied to VSS or VDD, OVR = [00],

outputs source/sink internal regulator

0mA set to 0.9V, 24.6

fSYS_CLK(MAX) =

7.3728MHz

www.analog.com Analog Devices | 15

Page16

MAX32672 High-Reliability, Tiny, Ultra-Low-Power

Arm Cortex-M4F Microcontroller

with 12-Bit, 1Msps ADC

Electrical Characteristics (continued)

(Limits are 100% tested at TA = +25°C and TA = +105°C. Limits over the operating temperature range and relevant supply voltage

range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested.

Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

OVR = [10],

internal regulator

Dynamic, IBRO set to 1.1V, 26.8

enabled, total fSYS_CLK(MAX) =

current into V 7.3728MHz

DD

pin, VDD = 1.8V, OVR = [01],

CPU in SLEEP internal regulator

mode, ECC set to 1.0V, 24.4

disabled, DMA fSYS_CLK(MAX) =

disabled, inputs 7.3728MHz

tied to VSS or VDD, OVR = [00],

outputs source/sink internal regulator

0mA set to 0.9V, 23

fSYS_CLK(MAX) =

7.3728MHz

Fixed, IBRO OVR = [10],

enabled, total internal regulator 423

current into VDD set to 1.1V

pin, VDD = 3.3V, OVR = [01],

CPU in SLEEP internal regulator 357

mode, ECC set to 1.0V

disabled, inputs

tied to VSS or VDD, OVR = [00],

outputs source/sink internal regulator 298

0mA set to 0.9V

IDD_FSLPS μA

Fixed, IBRO OVR = [10],

enabled, total internal regulator 376

current into VDD set to 1.1V

pin, VDD = 1.8V, OVR = [01],

CPU in SLEEP internal regulator 334

mode, ECC set to 1.0V

disabled, inputs

tied to VSS or VDD, OVR = [00],

outputs source/sink internal regulator 276

0mA set to 0.9V

SLEEP Mode Resume

Time tSLP_ONS fSYS_OSC = IBRO 1.1 μs

DEEPSLEEP Mode fast_wk_en = 1 182

Resume Time tDSL_ONS fSYS_OSC = IBRO μs

fast_wk_en = 0 319

BACKUP Mode Resume fSYS_OSC = IBRO, includes system

Time tBKU_ONS initialization and ROM execution time 1.08 ms

STORAGE Mode t fSYS_OSC = IBRO, includes system

Resume Time STO_ONS initialization and ROM execution time 1.08 ms

POWER / SINGLE-SUPPLY OPERATION (VDD ONLY)

Standby state with VDD = 3.3V 4.4

VDD Fixed Current, I full data retention

DEEPSLEEP Mode DD_FDSLS and 200KB SRAM μA

VDD = 1.8V 4.1

retained

www.analog.com Analog Devices | 16

Page17

MAX32672 High-Reliability, Tiny, Ultra-Low-Power

Arm Cortex-M4F Microcontroller

with 12-Bit, 1Msps ADC

Electrical Characteristics (continued)

(Limits are 100% tested at TA = +25°C and TA = +105°C. Limits over the operating temperature range and relevant supply voltage

range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested.

Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

0KB SRAM

retained, retention 0.4

regulator disabled

20KB SRAM

retained 1.09

VDD = 3.3V, RTC

disabled 40KB SRAM

retained 1.43

120KB SRAM

retained 2.35

200KB SRAM 3.26

VDD Fixed Current, retained

BACKUP Mode IDD_FBKUS μA

0KB SRAM

retained, retention 0.138

regulator disabled

20KB SRAM

retained 0.81

VDD = 1.8V, RTC

disabled 40KB SRAM

retained 1.15

120KB SRAM

retained 2.07

200KB SRAM

retained 2.97

VDD Fixed Current, VDD = 3.3V 0.397

STORAGE Mode IDD_FSTOS μA

VDD = 1.8V 0.123

www.analog.com Analog Devices | 17

Page18

MAX32672 High-Reliability, Tiny, Ultra-Low-Power

Arm Cortex-M4F Microcontroller

with 12-Bit, 1Msps ADC

Electrical Characteristics (continued)

(Limits are 100% tested at TA = +25°C and TA = +105°C. Limits over the operating temperature range and relevant supply voltage

range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested.

Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

POWER / DUAL-SUPPLY OPERATION (VDD AND VCORE); fSYS_OSC = IPO

OVR = [10], VCORE

Dynamic, IPO = 1.1V,

enabled, total f 61.5

SYS_CLK(MAX) =

current into VCORE 100MHz

pin, CPU in

ACTIVE mode, OVR = [01], VCORE

executing = 1.0V,

CoreMark, ECC fSYS_CLK(MAX) = 63.1

disabled, inputs 50MHz

tied to VSS or VDD, OVR = [00], VCORE

outputs source/sink = 0.9V, 53.2

0mA fSYS_CLK(MAX) =

12MHz

ICORE_DACTD μA/MHz

OVR = [10], VCORE

Dynamic, IPO = 1.1V, 50.3

enabled, total fSYS_CLK(MAX) =

current into V 100MHz

V CORE

CORE Current, pin, CPU in OVR = [01], V

ACTIVE Mode CORE

ACTIVE mode, = 1.0V,

executing While(1), f 50.5

SYS_CLK(MAX) =

ECC disabled, 50MHz

inputs tied to VSS OVR = [00], V

or VDD, outputs CORE

= 0.9V,

source/sink 0mA f 54

SYS_CLK(MAX) =

12MHz

Fixed, IPO OVR = [10], VCORE

enabled, total = 1.1V 497

current into VCORE OVR = [01], V

pin, CPU in CORE

= 1.0V 335

I ACTIVE mode

CORE_FACTD 0MHz execution, μA

ECC disabled, OVR = [00], V

inputs tied to V CORE

SS = 0.9V 187

or VDD, outputs

source/sink 0mA

www.analog.com Analog Devices | 18

Page19

MAX32672 High-Reliability, Tiny, Ultra-Low-Power

Arm Cortex-M4F Microcontroller

with 12-Bit, 1Msps ADC

Electrical Characteristics (continued)

(Limits are 100% tested at TA = +25°C and TA = +105°C. Limits over the operating temperature range and relevant supply voltage

range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested.

Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Dynamic, IPO OVR = [10],

enabled, total fSYS_CLK(MAX) = 0.005

current into VDD 100MHz

pin, VDD = 3.3V, OVR = [01],

CPU in ACTIVE f

mode, executing SYS_CLK(MAX) = 0.004

50MHz

CoreMark, ECC

disabled, inputs OVR = [00],

tied to VSS or VDD, f

outputs source/sink SYS_CLK(MAX) = 0.001

12MHz

0mA

Dynamic, IPO OVR = [10],

enabled, total fSYS_CLK(MAX) = 0.003

current into VDD 100MHz

pin, VDD = 1.8V, OVR = [01],

CPU in ACTIVE f = 0.0015

mode, executing SYS_CLK(MAX)

50MHz

CoreMark, ECC

disabled, inputs OVR = [00],

tied to VSS or VDD, f

outputs source/sink SYS_CLK(MAX) = 0.001

12MHz

VDD Current, ACTIVE 0mA

Mode IDD_DACTD μA/MHz

Dynamic, IPO OVR = [10],

enabled, total fSYS_CLK(MAX) = 0.005

current into VDD 100MHz

pin, VDD = 3.3V, OVR = [01],

CPU in ACTIVE f = 0.004

mode, executing SYS_CLK(MAX)

50MHz

While(1), ECC

disabled, inputs OVR = [00],

tied to VSS or VDD, f = 0.001

outputs source/sink SYS_CLK(MAX)

12MHz

0mA

Dynamic, IPO OVR = [10],

enabled, total fSYS_CLK(MAX) = 0.003

current into VDD 100MHz

pin, VDD = 1.8V, OVR = [01],

CPU in ACTIVE fSYS_CLK(MAX) = 0.0015

mode, executing 50MHz

While(1), ECC

disabled, inputs OVR = [00],

tied to VSS or VDD, f = 0.001

outputs source/sink SYS_CLK(MAX)

12MHz

0mA

www.analog.com Analog Devices | 19

Page20

MAX32672 High-Reliability, Tiny, Ultra-Low-Power

Arm Cortex-M4F Microcontroller

with 12-Bit, 1Msps ADC

Electrical Characteristics (continued)

(Limits are 100% tested at TA = +25°C and TA = +105°C. Limits over the operating temperature range and relevant supply voltage

range are guaranteed by design and characterization. Specifications marked GBD are guaranteed by design and not production tested.

Specifications to the minimum operating temperature are guaranteed by design and are not production tested.)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Fixed, IPO OVR = [10], VCORE

enabled, total = 1.1V 420

current into VDD OVR = [01], V

pin, V = 3.3V, CORE

DD = 1.0V 420

CPU in ACTIVE

mode 0MHz

execution, ECC

disabled, inputs OVR = [00], VCORE 420

tied to VSS or VDD, = 0.9V

outputs source/sink

0mA

IDD_FACTD μA

Fixed, IPO OVR = [10], VCORE

enabled, total = 1.1V 400

current into VDD OVR = [01], V

pin, V = 1.8V, CORE

DD = 1.0V 400

CPU in ACTIVE

mode 0MHz

execution, ECC

disabled, inputs OVR = [00], VCORE 400

tied to VSS or VDD, = 0.9V

outputs source/sink

0mA

www.analog.com Analog Devices | 20