1/31ページ

ダウンロード(3.1Mb)

TLP5214A/TLP5214/TLP5212/TLP5222

本資料はスマートゲートドライバーカプラーを動作させるために必要な設計情報をまとめた資料です。

TLP5214A/TLP5214/TLP5212/TLP5222 は表 1-1 の相違点にあるとおり、汎用のゲートドライバーカプラーにVCE(sat)検出・アクティブミラークランプ・FAULT 出力の機能を追加し、インバーター回路などで発生する過電流から IGBT やMOSFET を保護できるスマートゲートドライバー(SGD)カプラーです。

◆詳細はカタログをダウンロードしご覧いただくか、お気軽にお問い合わせ下さい。

このカタログについて

| ドキュメント名 | スマートゲートドライバーカプラーアプリケーションノート ー応用編ー |

|---|---|

| ドキュメント種別 | 製品カタログ |

| ファイルサイズ | 3.1Mb |

| 登録カテゴリ | |

| 取り扱い企業 | マウザー・エレクトロニクス (この企業の取り扱いカタログ一覧) |

この企業の関連カタログ

このカタログの内容

Page1

概要

Application Note

スマートゲートドライバーカプラー

TLP5214A/TLP5214/TLP5212/TLP5222

アプリケーションノート ー応用編ー

概要

本資料はスマートゲートドライバーカプラーを動作させるために必要な設計情報をまとめた資料です。

これは参考資料です。本資料での最終機器設計はしないでください。

© 20 21 -2 02 2 1 2022-04-21

Toshiba Electronic Devices & Storage Corporation Rev.2.0

Page2

目次

Application Note

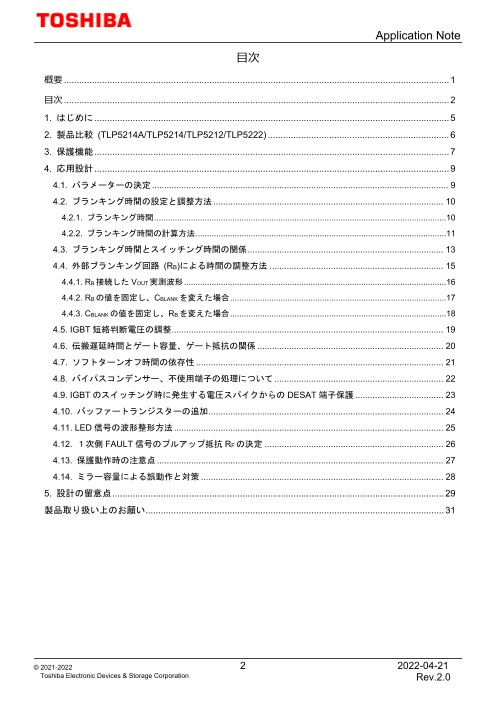

目次

概要 ....................................................................................................................................................... 1

目次 ....................................................................................................................................................... 2

1. はじめに ........................................................................................................................................... 5

2. 製品比較 (TLP5214A/TLP5214/TLP5212/TLP5222) ....................................................................... 6

3. 保護機能 ........................................................................................................................................... 7

4. 応用設計 ........................................................................................................................................... 9

4.1. パラメーターの決定 ......................................................................................................................... 9

4.2. ブランキング時間の設定と調整方法 .............................................................................................. 10

4.2.1. ブランキング時間 ...............................................................................................................................10

4.2.2. ブランキング時間の計算方法 .............................................................................................................11

4.3. ブランキング時間とスイッチング時間の関係 ................................................................................ 13

4.4. 外部ブランキング回路 (RB)による時間の調整方法 ....................................................................... 15

4.4.1. RB接続した VOUT実測波形 ..................................................................................................................16

4.4.2. RBの値を固定し、CBLANKを変えた場合 ..............................................................................................17

4.4.3. CBLANKの値を固定し、RBを変えた場合 ..............................................................................................18

4.5. IGBT 短絡判断電圧の調整 ............................................................................................................... 19

4.6. 伝搬遅延時間とゲート容量、ゲート抵抗の関係 ............................................................................ 20

4.7. ソフトターンオフ時間の依存性 ..................................................................................................... 21

4.8. バイパスコンデンサー、不使用端子の処理について ..................................................................... 22

4.9. IGBT のスイッチング時に発生する電圧スパイクからの DESAT 端子保護 .................................... 23

4.10. バッファートランジスターの追加 ................................................................................................ 24

4.11. LED 信号の波形整形方法 .............................................................................................................. 25

4.12. 1次側 FAULT 信号のプルアップ抵抗 RFの決定 ......................................................................... 26

4.13. 保護動作時の注意点 ..................................................................................................................... 27

4.14. ミラー容量による誤動作と対策 ................................................................................................... 28

5. 設計の留意点 .................................................................................................................................. 29

製品取り扱い上のお願い ..................................................................................................................... 31

© 20 21 -2 02 2 2 2022-04-21

Toshiba Electronic Devices & Storage Corporation Rev.2.0

Page3

Application Note

図目次

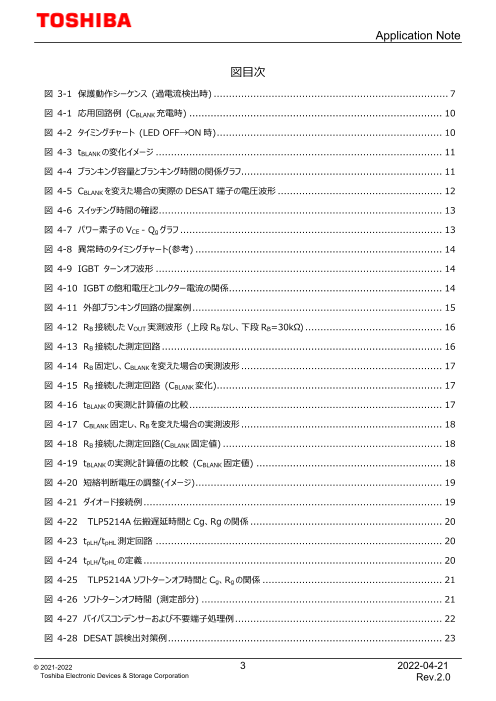

図 3-1 保護動作シーケンス (過電流検出時) ............................................................................. 7

図 4-1 応用回路例 (CBLANK 充電時) ................................................................................... 10

図 4-2 タイミングチャート (LED OFF→ON 時) .......................................................................... 10

図 4-3 tBLANK の変化イメージ .............................................................................................. 11

図 4-4 ブランキング容量とブランキング時間の関係グラフ .................................................................. 11

図 4-5 CBLANK を変えた場合の実際の DESAT 端子の電圧波形 ...................................................... 12

図 4-6 スイッチング時間の確認 ............................................................................................. 13

図 4-7 パワー素子の VCE - Qg グラフ ...................................................................................... 13

図 4-8 異常時のタイミングチャート(参考) ................................................................................. 14

図 4-9 IGBT ターンオフ波形 .............................................................................................. 14

図 4-10 IGBT の飽和電圧とコレクター電流の関係 ...................................................................... 14

図 4-11 外部ブランキング回路の提案例 .................................................................................. 15

図 4-12 RB 接続した VOUT 実測波形 (上段 RB なし、下段 RB=30kΩ) ............................................. 16

図 4-13 RB 接続した測定回路 ............................................................................................ 16

図 4-14 RB 固定し、CBLANK を変えた場合の実測波形 .................................................................. 17

図 4-15 RB 接続した測定回路 (CBLANK 変化).......................................................................... 17

図 4-16 tBLANK の実測と計算値の比較 ................................................................................... 17

図 4-17 CBLANK 固定し、RB を変えた場合の実測波形 .................................................................. 18

図 4-18 RB 接続した測定回路(CBLANK 固定値) ........................................................................ 18

図 4-19 tBLANK の実測と計算値の比較 (CBLANK 固定値) ............................................................. 18

図 4-20 短絡判断電圧の調整(イメージ) ................................................................................. 19

図 4-21 ダイオード接続例 .................................................................................................. 19

図 4-22 TLP5214A 伝搬遅延時間と Cg、Rg の関係 ............................................................... 20

図 4-23 tpLH/tpHL 測定回路 .............................................................................................. 20

図 4-24 tpLH/tpHL の定義 .................................................................................................. 20

図 4-25 TLP5214A ソフトターンオフ時間と Cg、Rg の関係 ........................................................... 21

図 4-26 ソフトターンオフ時間 (測定部分) ............................................................................... 21

図 4-27 バイパスコンデンサーおよび不要端子処理例 .................................................................... 22

図 4-28 DESAT 誤検出対策例 .......................................................................................... 23

© 20 21 -2 02 2 3 2022-04-21

Toshiba Electronic Devices & Storage Corporation Rev.2.0

Page4

Application Note

図 4-29 バッファートランジスター追加例 ................................................................................... 24

図 4-30 入力信号の波形整形方法例 ................................................................................... 25

図 4-31 1次側 FAULT 信号のプルアップ抵抗 RF 接続図 ............................................................. 26

図 4-32 内部回路図 (FAULT 時の動作経路) ........................................................................ 27

図 4-33 ミラー容量による誤動作の原因 .................................................................................. 28

図 4-34 負電源を使用する対策 .......................................................................................... 28

図 4-35 ゲート抵抗の調整 ................................................................................................. 28

図 4-36 ミラークランプ回路の使用 ......................................................................................... 28

表目次

表 1-1 製品相違点 ........................................................................................................... 5

表 2-1 製品比較表 ........................................................................................................... 6

表 3-1 保護動作と FAULT 信号のリセット タイミングチャート ............................................................. 8

表 4-1 トランジスターラインアップ ............................................................................................ 24

表 4-2 CMOS ロジック推奨製品 .......................................................................................... 25

表 4-3 TLP5214A 熱抵抗 ............................................................................................... 27

© 20 21 -2 02 2 4 2022-04-21

Toshiba Electronic Devices & Storage Corporation Rev.2.0

Page5

1. はじめに

Application Note

1. はじめに

TLP5214A/TLP5214/TLP5212/TLP5222 は表 1-1 の相違点にあるとおり、汎用のゲートドライバーカプラーに

VCE(sat)検出・アクティブミラークランプ・FAULT 出力の機能を追加し、インバーター回路などで発生する過電流から IGBT や

MOSFET を保護できるスマートゲートドライバー(SGD)カプラーです。

表 1-1 製品相違点

インバーター回路を必要とする汎用インバーター・太陽光発電パワーコンディショナーなどの産業機器を中心に、UPS や家庭

用蓄電池などの住宅設備機器まで幅広く使用できます。

© 20 21 -2 02 2 5 2022-04-21

Toshiba Electronic Devices & Storage Corporation Rev.2.0

Page6

2. 製品比較 (TLP5214A/TLP5214/TLP5212/TLP5222)

Application Note

2. 製品比較 (TLP5214A/TLP5214/TLP5212/TLP5222)

東芝の SGD カプラー製品の主な違いを表 2-1 に示します。

表 2-1 製品比較表

Item 記号 TLP5214A TLP5214 TLP5212 TLP5222 単位

動作温度 Topr -40 ~ 110 -40 ~ 110 -40 ~ 110 -40 ~ 110 ℃

ピーク出力電流 IOPH / IOPL ±4.0 ±4.0 ±2.5 ±2.5 A

(最大)

供給電流 ICC2 3.8 3.5 5 5 mA

(最大)

電源電圧 VCC2-VEE 15~30 15~30 15~30 15~30 V

スレッショルド入力電流 IFLH 6 6 6 6 mA

(最大)

DESAT スレッショルド VDESAT 6.5 6.5 6.6 6.6 V

(標準)

ブランキング容量充電電流 ICHG -0.24 -0.24 -0.26 -0.26 mA

(標準)

クランプ端子スレッショルド VtClamp 2.5 3.0 2.3 2.3 V

(標準)

伝搬遅延時間 tpLH / tpHL 150 150 250 250 ns

(最大) [注 1]

伝搬遅延スキュー[注 1] tpsk -80 ~ 80 -80 ~ 80 -150 ~ 150 -150 ~ 150 ns

DESAT 遅延 時 間 (90%) tDESAT(90%) 500 500 500 500 ns

(最大) [注 1]

DESAT 遅延 時 間 (10%) tDESAT(10%) 8.5 5 3 3 μs

(最大) [注 1]

DESAT 立ち上がり時 tDESAT(LEB) 1.1 - 1.27 1.4 μs

ブランキング時間

(標準) [注 1]

DESAT-フォルト間 tDESAT(FAULT) 550 500 500 500 ns

遅延時間 CF=open

(最大) [注 1]

DESAT 立 ち 下 が り 時 間 tDESAT(LOW) 200 200 172 167 ns

(標準) [注 1]

DESAT ミュート時間 tDESAT(MUTE) 7 ~ - 7 ~ - 5 ~ - 15 ~ 40 μs

(最小~最大)[注 1,2]

リセット時フォルト信号 tRESET(FAULT) 0.2 ~ 2 0.2 ~ 2 0.1 ~ 2.5 - μs

遅延時間[注 1]

保護機能 - UVLO, VCE(sat)検出, アクティブミラークランプ,FAULT 出力 -

FAULT 信号リセット方式[注 3] - LED トリガー型 自動復帰型 -

各特性値の詳細は製品のデータシートをご参照ください。

[注 1] 測定条件は以下のとおりです。

TLP5214A/TLP5214: Cg=25nF, Rg=10Ω

TLP5212/TLP5222: Cg=10nF, Rg=10Ω

[注 2] TLP5214A/TLP5214/TLP5212 と TLP5222 で tDESAT(MUTE) の定義が異なります。第 3 章の表 3-1 をご参照ください。

[注 3] 詳細は第 3 章で説明します。

TLP5214A/TLP5212/TLP5222 は立ち上がりブランキング時間を設定し、パワーデバイスの立ち上がり時などの誤検知

をしないようシャットダウン時間が遅めに設定された製品です。

また、TLP5214 は立ち上がりブランキング時間がなく、高速スイッチングする MOSFET や、保護動作にすばやく入る必要の

ある素子などに有利です。

© 20 21 -2 02 2 6 2022-04-21

Toshiba Electronic Devices & Storage Corporation Rev.2.0

Page7

3. 保護機能

Application Note

3. 保護機能

UVLO機能

UVLO (under voltage lock-out) 機能は、ゲートドライバーカプラー用電源(VCC2) がスレッショルド電圧を下回っ

た時のカプラーの誤出力を防止します。

電源投入後、VCC2 がまだ UVLO スレッショルド電圧に達していない間に、カプラーの出力はローレベルに保ちます。

同様に、VCC2 が UVLO スレッショルド電圧を下回った際に、カプラーが誤って出力されないように、カプラーの出力はシャッ

トダウンします。電源電圧が上昇し UVLO スレッショルド電圧を上回ると UVLO は解除されます。

VCE(sat)検出機能

VCE(sat)検出機能は、DESAT 端子により IGBT などのドライバー素子のコレクター-エミッター間電圧 (VCE)の飽和電

圧をモニターし、過電流を検出してシャットダウンさせる機能です。通常、IGBT が ON 状態では VCE は飽和電圧

VCE(sat) (約 2 V 以下)となりますが、過電流が発生すると、非飽和状態となり VCE(sat)が上昇します。VCE(sat)電圧が

規定値を超えた場合、FAULT 状態と判断して VOUT を緩やかにシャットダウンします。

アクティブミラークランプ機能

アクティブミラークランプ機能は、IGBT などのゲート-コレクター間に作られるミラー容量による電位の上昇を抑えるため、

ゲート抵抗などをバイパスし VEE に接続させる機能です。

FAULT出力機能

VCE(sat)検出機能で検知した FAULT 状態を 1 次側 (コントローラー側)に伝達させ、FAULT 信号を出力させる機

能です。

通常、IGBT が ON 状態では飽和電圧 VCE(sat)は 2V 程度になります。過電流が発生すると VCE(sat)が上昇し、

DESAT-VE ピン間電圧(VDESAT)が 6.5V(標準)以上になると、以下2つの動作を行います。

① VOUT をソフトシャットダウン (緩やかに OFF 状態へ遷移)し、過電流による IGBT の破壊を防止します。

② コントローラー側へ FAULT 信号を伝送します。

図 3-1 に過電流検出した際の保護動作シーケンスを示します。

通常、コントローラー側へ FAULT 信号をフィードバックし LED 信号/カプラー出力を停止するまでに数μs の時間がか

かりますが、TLP5214A/TLP5214/TLP5212/TLP5222 は 500 ns 以下で VOUT のシャットダウンを開始するため、

高速で安全性の高い保護回路を提供します。

図 3-1 保護動作シーケンス (過電流検出時)

© 20 21 -2 02 2 7 2022-04-21

Toshiba Electronic Devices & Storage Corporation Rev.2.0

Page8

Application Note

FAULT信号のリセット方法

SGD カプラーには保護動作発生後、入力 LED 信号を受け付けない時間 tDESAT(MUTE)が設けられています。保護動

作中の FAULT 信号のリセット方式は 2 種類あります。

① LED トリガー型:tDESAT(MUTE)経過後の入力 LED 信号でリセット。

TLP5214A/TLP5214/TLP5212 が該当します。

② 自動復帰型:tDESAT(MUTE)経過後自動的にリセット。

TLP5222 が該当します。

保護動作と FAULT 信号のリセットについて、表 3-1 のタイミングチャートを用いて説明します。

表 3-1 保護動作と FAULT信号のリセット タイミングチャート

LED トリガー型では FAULT 信号のリセットは入力 LED 信号に連動するため、コントローラーからの指令が必要です。

一方、自動復帰型では FAULT 信号は時間経過により自動的にリセットされるため、コントローラーでのシーケンス設定を

簡略化することができます。

© 20 21 -2 02 2 8 2022-04-21

Toshiba Electronic Devices & Storage Corporation Rev.2.0

Page9

4. 応用設計、4.1. パラメーターの決定

Application Note

4. 応用設計

4.1. パラメーターの決定

SGD カプラーを使用する際には以下のパラメーターを決定します。

1.ゲート抵抗

ゲートドライバー製品の最大定格 (IOP)以下になるようにゲート抵抗を設定します。なおこの値はドライバー側では電流

および電力定格が製品の最大定格内になる必要があり、また、パワーデバイス (IGBT / MOSFET)側はターンオン時間

やターンオフ時間の速さに影響しますので、双方を考慮して適切な値に設計します。

2.ブランキング時間

製品に電源を投入し、入力信号をいれると製品が動作し、VOUT からゲートドライブ用の電流が出力されます。同時に

DESAT 機能が動作を開始しますが、パワーデバイスのターンオン時間が長い製品の場合、VCE 間電圧が下がりきる前に

DESAT 機能が電圧レベルを検知しシャットダウンモードに入ります。

電圧検知のタイミングはブランキングコンデンサーや周辺回路で調整します。

3.短絡判断電圧

パワーデバイスの異常 (短絡状態など)を検知するため、DESAT 端子を使用します。製品の短絡判断をするため、電

圧を監視しており 6.5 V (標準値)を越えると製品はシャットダウンモードに入ります。パワー素子の短絡判断電圧をより引

き下げたい場合は、DESAT ダイオードとは別にツェナーダイオードや SBD を追加して調整します。

4.1 次側 FAULT 信号のプルアップ抵抗

フィードバック回路の出力はオープンコレクターとなっており、プルアップ抵抗を接続します。抵抗の設定値によっては

FAULT からの復帰時間が長くなります。ご使用のシステムや電源に応じて抵抗を調整します。

5.誤動作対策

各定数を設定後、必要に応じて誤動作対策部品を追加します。

© 20 21 -2 02 2 9 2022-04-21

Toshiba Electronic Devices & Storage Corporation Rev.2.0

Page10

4.2. ブランキング時間の設定と調整方法、4.2.1. ブランキング時間

Application Note

4.2. ブランキング時間の設定と調整方法

4.2.1. ブランキング時間

図 4-1 は IGBT を駆動させる際の応用回路例で、図 4-2 はスイッチング時のタイミングチャートを示したものです。LED 入

力電流 (IF)を OFF→ON にすると出力端子 (VOUT)の電圧が上昇し、外付け IGBT がターンオン動作を始めます。同時

に、外付け IGBT のコレクター-エミッター間電圧 (VCE)をモニターするために DESAT 端子からブランキング容量充電電流

ICHG が出力され、DESAT 端子電圧が上昇し始めます。なお TLP5214A/TLP5212/TLP5222 の DESAT 端子の立ち

上がりには誤動作防止の期間 tDESAT(LEB)が設定されています。

正常時の IGBT のターンオン動作時においては、誤動作防止のため VCE が IGBT の短絡判断電圧 Vth(IGBT)以下になる

までの間、保護回路である DESAT 機能を無効にする必要があります。図 4-2 で示すとおり、IF の立ち上がりから DESAT 電

圧が 6.5 V (標準値)に達するまでの時間をブランキング時間 tBLANK と呼び、この時間は DESAT-VE 端子間に挿入するコ

ンデンサーCBLANK の値で調整できます。

正常動作状態では、tBLANK は VCE が Vth(IGBT)に達する時間 tth よりも長く、IGBT などの短絡許容時間 tSC よりも短く

なるように設定する必要があります。

図 4-1 応用回路例

図 4-2 タイミングチャート

(CBLANK充電時) (LED OFF→ON時)

© 20 21 -2 02 2 10 2022-04-21

Toshiba Electronic Devices & Storage Corporation Rev.2.0

ー

Page11

4.2.2. ブランキング時間の計算方法

Application Note

4.2.2. ブランキング時間の計算方法

tBLANK は下式のように CBLANK、VDESAT、ICHG 、tDESAT(LEB)により計算でき

ます。

tBLANK = CBLANK × VDESAT / ICHG + tDESAT(LEB)

ここで TLP5214A を例として、VDESAT、ICHG、tDESAT(LEB)は標準値で、それ

ぞれ 6.5 V、240 μA、1.1 μs です。

tBLANK の計算例を示します。

CBLANK として 200 pF を使う場合、tBLANK は次のように計算します。

tBLANK = 200 × 10-12 F × 6.5 V / (240 × 10-6) A +1.1 μs

= 6.5 μs

CBLANK と tBLANK の関係は図 4-4 のグラフとなります。また CBLANK を大きくす

ることで、DESAT 端子間電圧の立ち上がり時の傾きが変わり、過電流保護動作

が有効になるまでの時間が長くなります (図 4-3)。実際には CBLANK だけでなく、 図 4-3 tBLANKの変化イメージ

接続したダイオードの寄生容量などが tBLANK に影響しますので注意が必要です。

CBLANK の値を調整することで、過電流保護検知が誤動作せず、パワー素子の短絡許容時間内となる tBLANK の時間に

設定します。

図 4-4 ブランキング容量とブランキング時間の関係グラフ

© 20 21 -2 02 2 11 2022-04-21

Toshiba Electronic Devices & Storage Corporation Rev.2.0

Page12

Application Note

(参考)CBLANKを変えた時の代表波形

TLP5214A の LED を ON させ、DESAT 端子、VOUT 端子をモニターした実際の波形を図 4-5 に示します。

TLP5214A CBLANK 無し TLP5214A CBLANK =100pF

図 4-5 CBLANKを変えた場合の実際の DESAT端子の電圧波形

このように CBLANK によって tBLANK が変わることが確認できます。実応用上は、DESAT ライン上に接続したダイオードの容

量や回路の浮遊容量などが含まれるため、設計の際にはそれらを含めて見積もる必要があります。なお本評価に使用した基

板の容量は 25 pF 程度です (波形取得時にはプローブ容量も追加されます)。

© 20 21 -2 02 2 12 2022-04-21

Toshiba Electronic Devices & Storage Corporation Rev.2.0

Page13

4.3. ブランキング時間とスイッチング時間の関係

Application Note

4.3. ブランキング時間とスイッチング時間の関係

SGD カプラーの LED を ON して IGBT がターンオンするまでのスイッチング時間は、tBLANK 以下であることが必要です(図

4-6)。ここで TLP5214A を例としてブランキング時間とスイッチング時間の関係を説明します。

条件: TLP5214A の tpLH + IGBT の tON* = スイッチング時間 < tBLANK *(tth ≒ tON とする)

tpLH : TLP5214A のデータシートより 150 ns (max)

tON : IGBT の Qg 、TLP5214A の出力電流 IO から推定します。 (計算式;tON = Qg / IO)

ここで例として IGBT GT30J341 を VGE = 15 V , IO = 1.5 A でスイッチングさせる場合、

データシートの VCE, VGE - Qs 特性から Qs は 130 nC (図 4-7 参照)なので

tON = 130 nC / 1.5 A ≒ 87 ns

従ってスイッチング時間は

tON = 150 ns + 87 ns

= 237 ns < 6.5 μs (p.11 に参照)

となり、tBLANK 以下であることが確認できます。

図 4-6 スイッチング時間の確認 図 4-7 パワー素子の VCE - Qgグラフ

© 20 21 -2 02 2 13 2022-04-21

Toshiba Electronic Devices & Storage Corporation Rev.2.0

Page14

Application Note

(参考) 異常時のタイミングチャート

正常時のスイッチングと異常時における各端子 (IF, VO, IO, VCE, DESAT)の波形を図 4-8 に示します。

SGD カプラーに IF 入力後、VO が出力され、IGBT のゲートをドライブします。

IGBT が正常にスイッチングすると、VCE 電圧が IGBT の飽和電圧まで下がります。同時にその端子をモニターしている

DESAT 端子の電圧も同様に下がり、飽和電圧と DESAT ダイオードの VF を合計した電圧値まで下がります。

V IC

CE

※通常のターンオフは図 4-9 のような

波形となります。

図 4-8 異常時のタイミングチャート(参考)

次にアーム短絡などの異常が発生した場合①、ショート状態によって電流 IC (青線)が増加し過電流状態②となります。

IGBT の電流が増加すると IGBT の VCE(sat)は電流につられて上昇③ (図 4-10)、同時に DESAT 端子電圧も上昇しま

す④。その後DESAT端子電圧がしきい値 (標準値6.5 V)を超えると、カプラーは短絡状態と判断し、保護モードに入り⑤、

カプラーは VO、IO をシャットダウンさせますが⑥、急峻なオフなどでノイズなどを発生させないよう、緩やかにシャットダウンさせます

⑦。なお異常状態を検知したカプラーは、FAULT 状態であることを入力側に伝えるため、内部の LED を点灯させ、FAULT

状態であることを出力します。

図 4-9 IGBT ターンオフ波形 図 4-10 IGBTの飽和電圧とコレクター電流の関係

© 20 21 -2 02 2 14 2022-04-21

Toshiba Electronic Devices & Storage Corporation Rev.2.0

Page15

4.4. 外部ブランキング回路 (RB)による時間の調整方法

Application Note

4.4. 外部ブランキング回路 (RB)による時間の調整方法

スイッチング時のノイズ耐性強化のために CBLANK を大きくすると、充電時間が長くなるため tSC 以内に保護動作が機能しな

い可能性があります。そこで、図 4-11 のように外部抵抗を用いて CBLANKへの充電電流を増やすことで保護動作を確実に行

うことが出来ます。具体的には出力 VOUT から DESAT 端子間に外部抵抗 (RB)を追加して外部電流 (IB)を引き込み、

ICHG を補完します。

CBLANK への充電電流を RB によってコントロールできるため、より自由度の高いブランキング時間の設定ができるようになりま

す。 SGD カプラー

1uF CBLANK

I R D

CHG DESAT DESAT P

1uF IB

1uF

RB

Rg

25nF 17V

10V N

図 4-11 外部ブランキング回路の提案例

ブランキングコンデンサーに印加される電圧は次のように表すことができます。

VI = VOUT - VE

= RB × i(t) + ∫(ICHG + i(t))dt / CBLANK

i(t) = (VI/RB + ICHG) exp(- t/(CBLANK × RB)) - ICHG

VDESAT (t) = VI - RB × i(t)

= VI - (VI + RB × ICHG )exp (- t / (CBLANK × RB)) + RB × ICHG

この式よりブランキング時間は

tBLANK = -CBLANK × RB × log(1 - VDESAT / (VI + RB × ICHG)) となりますが、

TLP5214A/TLP5212/TLP5222 の場合、DESAT 立ち上がり時ブランキング時間 tDESAT(LEB)を加えて計算します。

計算例として、CBLANK = 300 pF、RB = 30 kΩ、VOUT = 17 V、VEE = -10 V、VE ≒ 0 V とし、

TLP5214A のデータシートより、VDESAT = 6.5 V、ICHG = 0.24 mA、tDESAT(LEB) = 1.1 μs を使って

-12 3 3 -6 -6

t = -300 × 10 × 30 × 10 × log(1-6.5 / (17 + 30 × 10 × 240 × 10 ) + 1.1 × 10

-9 -6

= -9000 × 10 × log (1 - 6.5 / (17 + 7.2)) + 1.1 × 10

-6 -6

= -9 × 10 × log (0.7314) + 1.1 × 10

-6 -6

= 2.815 × 10 + 1.1 × 10

よって tBLANK は 3.9 μs となります。

© 20 21 -2 02 2 15 2022-04-21

Toshiba Electronic Devices & Storage Corporation Rev.2.0

Page16

4.4.1. RB接続したVOUT実測波形

Application Note

4.4.1. RB接続した VOUT実測波形

RB を接続した際の実測波形を図 4-12 に示します。評価は図 4-13 に示す回路図を用い、CBLANK= 125 pF (外付け

100 pF+ 評価基板上の容量 25 pF) を接続した状態で、RB = 30 kΩの抵抗がある場合とない場合で確認しています。

(VCC2 = 17 V、VEE= -10 V)

RB を接続しない場合の tBLANK は 4.5 μs ですが、接

続した場合は 2.5 μs と、RB を経由して流れる IB により

ブランク時間が短くなっています。

RB 無し

これにより CBLANK をより大きな値に設定しても、短絡保

護時間を超えない設計ができるようになります。

RB =30kΩ

図 4-12 RB接続した VOUT実測波形 (上段 RBなし、下段 RB=30kΩ)

※本評価に使用した基板の容量 25pF 程度(SBD, ツェナーダイオード含む)

図 4-13 RB接続した測定回路

© 20 21 -2 02 2 16 2022-04-21

Toshiba Electronic Devices & Storage Corporation Rev.2.0

Page17

4.4.2. RBの値を固定し、CBLANKを変えた場合

Application Note

4.4.2. RBの値を固定し、CBLANKを変えた場合

次に CBLANK の影響を確認するため、CBLANK を 100 pF から 680 pF まで変えたときの波形を図 4-14 に示します。

図 4-14 RB固定し、CBLANKを変えた場合の実測波形

この波形の測定回路図は図 4-15 に示すとおりで、RB は 30 kΩを使用しています。接続するコンデンサーを CBLANK=

100 ~ 3000 pF (および評価基板上の容量 25 pF)で条件を振り、VCC2 = 17 V、VEE = -10 V の電圧で測定してい

ます。

※本評価に使用した基板の容量 25pF 程度(SBD, ツェナーダイオード含む)

図 4-15 RB接続した測定回路 (CBLANK変化)

CBLANK を変えた条件で測定した tBLANK と

tBLANK = -CBLANK × RB × log(1 - VDESAT/(VI + RB ×

ICHG) )・・・p.15

の計算式で求められる tBLANK を比較したグラフを図 4-16 に示します。

CBLANK = 2000 pF まではほぼ計算とおりとなると予想できます。ただ

し、大きなコンデンサーを使用する場合、IGBT の短絡耐量時間によって

制限されますので、適切な容量のコンデンサーを選択してください。

図 4-16 tBLANKの実測と計算値の比較

© 20 21 -2 02 2 17 2022-04-21

Toshiba Electronic Devices & Storage Corporation Rev.2.0

Page18

4.4.3. CBLANKの値を固定し、RBを変えた場合

Application Note

4.4.3. CBLANKの値を固定し、RBを変えた場合

次に RB の条件を変えた場合の実測波形を図 4-17 に示します。

図 4-17 CBLANK固定し、RBを変えた場合の実測波形

測定回路は図 4-18 に示すとおりで、外付けの CBLANK = 330 pF (基板容量除く)で固定し、RB の条件を

330Ω ~ 30 kΩに変化させています。なお電圧条件は VCC2 = 17 V、VEE = -10 V で測定しています。

※本評価に使用した基板の容量 25pF 程度(SBD, ツェナーダイオード含む)

図 4-18 RB接続した測定回路(CBLANK固定値)

RB を変えた条件で測定した tBLANK と式 (p.15)で計

算される tBLANK を比較したグラフを図 4-19 に示します。

低い抵抗値を用いることで tBLANKを短く設定できますが、

VOUT が出力されている間、RB に流れる電流が大きくなる

ため消費電流の増加に注意してください。

図 4-19 tBLANKの実測と計算値の比較 (CBLANK固定値)

© 20 21 -2 02 2 18 2022-04-21

Toshiba Electronic Devices & Storage Corporation Rev.2.0

Page19

4.5. IGBT短絡判断電圧の調整

Application Note

4.5. IGBT短絡判断電圧の調整

DESAT 端子は IF 入力時に端子にかかる電圧をチェックし

ます。端子電圧 VDESAT が 6.5 V (標準値)を越えると

DESAT 回路が動作し、本製品は保護動作に入ります。ここ

でパワーデバイスの VCE はダイオードや抵抗を経由して確認し

ていますので、実際の IGBT の VCE とは差があります。図 4-

20 はダイオードなどを接続した際に変化する短絡判断電圧の

調整方法を示したものです。

IGBT 側の電圧を基準としたときの短絡判断電圧を

Vth(IGBT)と定義した場合、使用する IGBT の安全動作領域

を考慮して Vth(IGBT)を下げる必要がある場合、またはより低

い電圧で保護動作をさせたい場合、図4-21 のように 図 4-20 短絡判断電圧の調整(イメージ)

DESAT ダイオードを複数接続し、複数素子の VF による電圧

降下を利用し、Vth(IGBT)を引き下げて New Vth(IGBT)として設定することが可能です (方法①)。また、同様にツェナーダイオ

ードを使用することで、微調整も可能です (方法②)。

方法①の場合 New Vth(IGBT) = VDESAT – (n × VF + RDESAT × ICHG) n: ダイオードの数

方法②の場合 New Vth(IGBT) = VDESAT – (VF + VZ + RDESAT × ICHG) VZ: ツェナー電圧

例えば、方法①で、ダイオード (VF = 0.4 V@240 μA) を 3 個、RDESAT として 100 Ω を使用した場合、

New Vth(IGBT) = 6.5 – (3 × 0.4 V + 100 Ω × 240 μA) ≒ 5.3 V とすることができます。

SGD カプラー

図 4-21 ダイオード接続例

なお、正常動作時には DESAT ダイオードに順電流が流れ、IGBT の VCE を監視しています。ただし大電力のアプリケーシ

ョンではスイッチングの際の逆回復電流などにより DESAT 電圧の誤検出を誘発します。この逆回復電流を最小化させるため

に、寄生容量の小さい FRD を推奨します。

© 20 21 -2 02 2 19 2022-04-21

Toshiba Electronic Devices & Storage Corporation Rev.2.0

Page20

4.6. 伝搬遅延時間とゲート容量、ゲート抵抗の関係

Application Note

4.6. 伝搬遅延時間とゲート容量、ゲート抵抗の関係

図4-22 に、TLP5214A を例として、伝搬遅延時間 tpLH / tpHL と Cg、Rg の関係を示します。また評価回路(図 4-

23)や波形の測定場所(図 4-24)は下図のとおりとなっておりますが、伝搬遅延時間は Cg、Rg にはほとんど依存しません。

図 4-22 TLP5214A伝搬遅延時間と Cg、Rgの関係

図 4-24 tpLH/tpHL測定回路 図 4-23 tpLH/tpHLの定義

© 20 21 -2 02 2 20 2022-04-21

Toshiba Electronic Devices & Storage Corporation Rev.2.0