Page1

MCX N94x、セキュア・コネクテッド・エッジの普及がかつてないほど拡大するなか、エッジ向けの製品を開発する設計エンジニアは、これまで以上に多くの課題に直面しています。たとえば、パフォーマンス上の 制約の克服、人工知能 (AI) および機械学習 (ML) 機能の統合と高速化、電力効率の向上、コネクティビティ・オプションの拡大、セキュリティの確保などの課題があります。これらのニーズに対処するため、NXPではインダストリアル&IoTエッジ・コンピューティングの時代に適したMCXポートフォリオを開発しました。、MCX N94x MCUファミリの紹介

ホワイト・ペーパー

MCX N94x

MCX N94x MCU:より多くの

インテリジェンスをエッジに導入

セキュア・コネクテッド・エッジの普及がかつてないほど拡大するなか、エッジ向けの製品を開発する

設計エンジニアは、これまで以上に多くの課題に直面しています。たとえば、パフォーマンス上の

制約の克服、人工知能 (AI) および機械学習 (ML) 機能の統合と高速化、電力効率の向上、コネクティ

ビティ・オプションの拡大、セキュリティの確保などの課題があります。これらのニーズに対処するた

め、NXPではインダストリアル&IoTエッジ・コンピューティングの時代に適したMCXポートフォリオ

を開発しました。

NXPの多様で広範なマイクロコントローラ (MCU) 製品ライ MCX Nシリーズは、パワフルな演算およびデータ処理能

ンナップに追加されたMCXは、優れた拡張性、シンプルなシ 力をコネクテッド・エッジにもたらします。エッジで生成

ステム設計手法、開発者本位のエクスペリエンスを備えた、 されるデータの量はますます増加しているため、クラウド

複数のシリーズで提供されています。このホワイト・ と共有する前に、より多くのデータをエッジ・デバイス上

ペーパーでは、セキュア・コネクテッド・エッジの設計上の でローカルに処理することが、極めて重要になっています。

課題に取り組むうえで、MCX Nシリーズ(特にMCX N94x また、開発者はエッジに接続されたシステムを安全かつセ

MCU)がどのように役立つのかを解説します。 キュアな状態に保つ必要もあります。MCX N94xファミ

リは、マルチコアのパフォーマンス、インテリジェントな

MCX N94x MCUファミリの紹介 自律型ペリフェラル、セキュア・バイ・デザイン手法によ

る高度なセキュリティでこれらのニーズを満たし、絶えず

MCXポートフォリオは、ホーム・コントロール、スマート家 変化するエッジ・デバイスのセキュリティ要件に対処しま

電、ファクトリ・オートメーション、電力&エネルギー・イ す。

ンフラストラクチャ、その他のインダストリアル&IoTアプ MCX N94x MCUには、デュアルコア・アーキテクチャ、

リケーション向けに統一されたMCUプラットフォームを提供 オンチップ・アクセラレータ、コネクティビティ、セキュ

します。この32ビットArm® Cortex®-MベースのMCUから リティ機能のほか、センシング、制御、ヒューマン・マシ

なる広範なポートフォリオには、エントリレベルから高性能 ン・インターフェース (HMI) 向けのアナログおよびデジ

および高集積まで、さまざまな製品が用意されています。 タル・ペリフェラルが多数組み込まれています。

Page2

MCX N94xのブロック図、パフォーマンス:より多くのインテリジェンスを エッジに導入、プライマリArm Cortex-M33

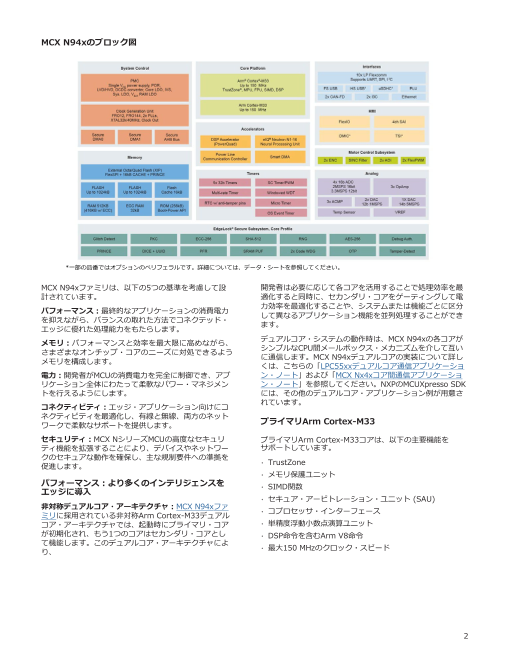

MCX N94xのブロック図

*一部の品番ではオプションのペリフェラルです。詳細については、データ・シートを参照してください。

MCX N94xファミリは、以下の5つの基準を考慮して設 開発者は必要に応じて各コアを活用することで処理効率を最

計されています。 適化すると同時に、セカンダリ・コアをゲーティングして電

パフォーマンス:最終的なアプリケーションの消費電力 力効率を最適化することや、システムまたは機能ごとに区分

を抑えながら、バランスの取れた方法でコネクテッド・ して異なるアプリケーション機能を並列処理することができ

エッジに優れた処理能力をもたらします。 ます。

メモリ:パフォーマンスと効率を最大限に高めながら、 デュアルコア・システムの動作時は、MCX N94xの各コアが

さまざまなオンチップ・コアのニーズに対処できるよう シンプルなCPU間メールボックス・メカニズムを介して互い

メモリを構成します。 に通信します。MCX N94xデュアルコアの実装について詳し

くは、こちらの「LPC55xxデュアルコア通信アプリケーショ

電力:開発者がMCUの消費電力を完全に制御でき、アプ ン・ノート」および「MCX Nx4xコア間通信アプリケーショ

リケーション全体にわたって柔軟なパワー・マネジメン ン・ノート」を参照してください。NXPのMCUXpresso SDK

トを行えるようにします。 には、その他のデュアルコア・アプリケーション例が用意さ

コネクティビティ:エッジ・アプリケーション向けにコ れています。

ネクティビティを最適化し、有線と無線、両方のネット

ワークで柔軟なサポートを提供します。 プライマリArm Cortex-M33

セキュリティ:MCX NシリーズMCUの高度なセキュリ プライマリArm Cortex-M33コアは、以下の主要機能を

ティ機能を拡張することにより、デバイスやネットワー サポートしています。

クのセキュアな動作を確保し、主な規制要件への準拠を

促進します。 • TrustZone

• メモリ保護ユニット

パフォーマンス:より多くのインテリジェンスを

エッジに導入 • SIMD関数

• セキュア・アービトレーション・ユニット (SAU)

非対称デュアルコア・アーキテクチャ:MCX N94xファ

ミリに採用されている非対称Arm Cortex-M33デュアル • コプロセッサ・インターフェース

コア・アーキテクチャでは、起動時にプライマリ・コア • 単精度浮動小数点演算ユニット

が初期化され、もう1つのコアはセカンダリ・コアとし • DSP命令を含むArm V8命令

て機能します。このデュアルコア・アーキテクチャによ

り、 • 最大150 MHzのクロック・スピード

2

Page3

MCX N94x eIQ® Neutronニューラル・プロセッシング・ユニット (NPU)

用意されているため、開発者がカスタム命令を記述する必要

はありません。また、SDK APIを利用すれば、PowerQuad

用の命令やレジスタ設定を選択する作業も不要になります。

PowerQuadアクセラレータは、高度なフィルタの実行時に

使用するCPUサイクル数が少ないため、パフォーマンスと効

率性が高まります。PowerQuadのパフォーマンス・ベンチ

マークの詳細については、こちらのアプリケーション・ノー

トをご覧ください。

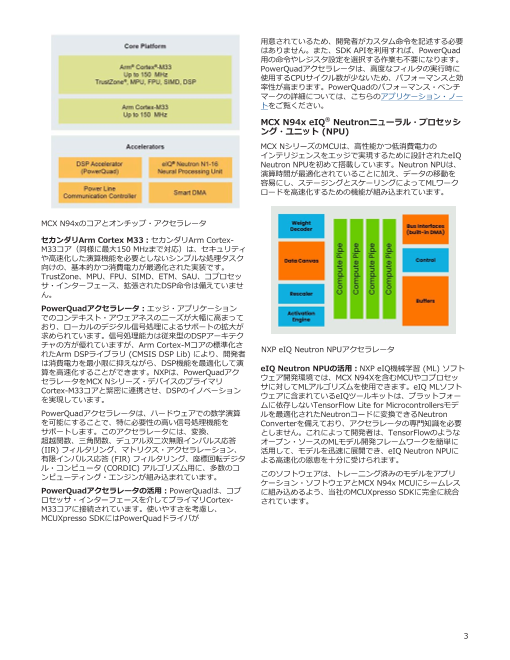

MCX N94x eIQ® Neutronニューラル・プロセッシ

ング・ユニット (NPU)

MCX NシリーズのMCUは、高性能かつ低消費電力の

インテリジェンスをエッジで実現するために設計されたeIQ

Neutron NPUを初めて搭載しています。Neutron NPUは、

演算時間が最適化されていることに加え、データの移動を

容易にし、ステージングとスケーリングによってMLワーク

ロードを高速化するための機能が組み込まれています。

MCX N94xのコアとオンチップ・アクセラレータ

セカンダリArm Cortex M33:セカンダリArm Cortex-

M33コア(同様に最大150 MHzまで対応)は、セキュリティ

や高速化した演算機能を必要としないシンプルな処理タスク

向けの、基本的かつ消費電力が最適化された実装です。

TrustZone、MPU、FPU、SIMD、ETM、SAU、コプロセッ

サ・インターフェース、拡張されたDSP命令は備えていませ

ん。

PowerQuadアクセラレータ:エッジ・アプリケーション

でのコンテキスト・アウェアネスのニーズが大幅に高まって

おり、ローカルのデジタル信号処理によるサポートの拡大が

求められています。信号処理能力は従来型のDSPアーキテク

チャの方が優れていますが、Arm Cortex-Mコアの標準化さ

れたArm DSPライブラリ (CMSIS DSP Lib) により、開発者 NXP eIQ Neutron NPUアクセラレータ

は消費電力を最小限に抑えながら、DSP機能を最適化して演

算を高速化することができます。NXPは、PowerQuadアク eIQ Neutron NPUの活用:NXP eIQ機械学習 (ML) ソフト

セラレータをMCX Nシリーズ・デバイスのプライマリ ウェア開発環境では、MCX N94Xを含むMCUやコプロセッ

Cortex-M33コアと緊密に連携させ、DSPのイノベーション サに対してMLアルゴリズムを使用できます。eIQ MLソフト

を実現しています。 ウェアに含まれているeIQツールキットは、プラットフォー

ムに依存しないTensorFlow Lite for Microcontrollersモデ

PowerQuadアクセラレータは、ハードウェアでの数学演算 ルを最適化されたNeutronコードに変換できるNeutron

を可能にすることで、特に必要性の高い信号処理機能を Converterを備えており、アクセラレータの専門知識を必要

サポートします。このアクセラレータには、変換、 としません。これによって開発者は、TensorFlowのような

超越関数、三角関数、デュアル双二次無限インパルス応答 オープン・ソースのMLモデル開発フレームワークを簡単に

(IIR) フィルタリング、マトリクス・アクセラレーション、 活用して、モデルを迅速に展開でき、eIQ Neutron NPUに

有限インパルス応答 (FIR) フィルタリング、座標回転デジタ よる高速化の恩恵を十分に受けられます。

ル・コンピュータ (CORDIC) アルゴリズム用に、多数のコ

ンピューティング・エンジンが組み込まれています。 このソフトウェアは、トレーニング済みのモデルをアプリ

ケーション・ソフトウェアとMCX N94x MCUにシームレス

PowerQuadアクセラレータの活用:PowerQuadは、コプ に組み込めるよう、当社のMCUXpresso SDKに完全に統合

ロセッサ・インターフェースを介してプライマリCortex- されています。

M33コアに接続されています。使いやすさを考慮し、

MCUXpresso SDKにはPowerQuadドライバが

3

Page4

Smart DMA、MCX N94xのパフォーマンス概要、メモリ・アーキテクチャ:効率的なパフォーマンスの実現

eIQ Neutron NPUのメリット:クラス最高のMLアクセ Smart DMAの活用方法:MCUXpresso SDKには、

ラレータとして、リソースや電力に制約のあるエッジ・ Smart DMA向けの一連のコンパイル済み関数が用意され

デバイス向けのTinyMLの能力を増強します。高度な ています。また、追加の関数やカスタマイズした関数を

ディープラーニング・モデルの導入、アクセス制御のた 開発するために、お客様がアクセスをリクエストすること

めの顔認識や音声認識の追加、ホーム・セキュリティ・ もできます。詳細については、NXPの営業担当者までお問

システム用のバッテリー駆動ガラス破損検出器の作成、 い合わせください。

モータ制御の予知保全用の振動センサの開発、バイオ・

センサを搭載したスマート・ウェアラブル・デバイスの MCX N94xのパフォーマンス概要

設計など、無限の可能性を秘めています。

MCX N94xには、動作速度最大150 MHzの2つのArm

Cortex-M33コアを含む、アクセス可能なプログラマブル・

コアが組み込まれています。メインArm Cortex-M33コア

で動作するフィルタの実行を最適化するためにPowerQuad

を含む追加のアクセラレータを備え、ML処理の高速化と他

のCPUの負荷軽減のためにeIQ Neutron NPUを備えていま

す。Smart DMAは、基本的な機能の負荷をさらに軽減でき

るほか、必要に応じて独自の機能向けに設定することもできま

す。詳細については、NXPの営業担当者までお問い合わせくだ

さい。これらのコアとアクセラレータが連携することで、1つ

のMCUでの処理性能が大幅に高まるため、エッジ・データをよ

り効率的に収集、処理できるようになります。

eIQ Neutron NPUによって達成された高速化 メモリ・アーキテクチャ:効率的なパフォーマンスの

実現

Smart DMA MCX Nシリーズのメモリ・アーキテクチャによって柔軟性

Smart DMAコアは、高度に最適化されたI/O処理向けに が高まるため、開発者はコスト、基板面積、電力効率のバ

設計されている縮小命令セット処理エンジンです。Arm ランスを維持しながら、複数のコアのパフォーマンスを最

コアと同様にシステム・バス上のすべてのメモリとペリ 大限に引き出すことができます。そのため、MCX Nシリー

フェラルにアクセスできます。Smart DMAは、システム ズのMCUは、十分なオンチップ・メモリ、RAM、および組

のArmプロセッサの負荷を軽減するためにイベントまた 込みフラッシュに加え、外部のRAMやフラッシュ・メモリ

はI/O駆動型の処理を実行するコアであり、以下のタスク を使用可能にするFlexSPIインターフェースを備えていま

のパフォーマンスを最適化するように設計されています。 す。また、パーティションに分割されたメモリも、開発者

が消費電力を最適化しながら複数のアプリケーションを実

• ステート・マシンの制御 行するのに役立ちます。

• ブール値の検出 内部SRAM:MCX N94xでは、ECCが有効化されていない

• 場合に最大512 KBのSRAMを使用できます。すべての

単純なタスク SRAMでECCが有効化されている場合は、最大416 KBの

• DMA機能 SRAMを使用できます。

• Armコアでの割込み負荷の軽減 SRAMは、9個の個別のバンク(RAMA~GとRAMX)に分

• 汎用I/Oのストリーミング 割されています。このパーティション分割により、使用さ

• 一般的なI/O処理 れていないRAMバンクの電源をオフにできるため、エネル

ギー効率が向上し、開発者がより効率的にRAMメモリを管

• パラレル・カメラやLCDインターフェースなどの 理できます。

I/Oを介したプロトコル・エミュレーション

• シフトベースのアルゴリズム計算 96 KBのRAMXアレイは、Cortex-M33コアのC-AHB

Codeバスに接続されています。この接続により、

• 大規模なデータ操作 フラッシュ・メモリに伴う遅延に対処する余裕のない

時間的要件の厳しいコードも配置できるようになるため、

Smart DMAとeDMA:Smart DMAを拡張DMA (eDMA) パフォーマンスが向上します。そのため重要なコード・セ

と混同してはいけません。eDMAは、ホスト・プロセッサの グメントを効率的に実行できます。フラッシュ・メモリ上

介入を最小限に抑えながら複雑なデータ転送を実行できる、 にあるCPU0コードとSRAMX上にあるCPU1コードを、両

より一般的なDMAモジュールです。eDMAエンジンは、 方のCortex-M33コアで同時に実行する場合、バス接続が

ソース・アドレスおよびデスティネーションの計算と、 不要であるため、チップの全体的なコンピューティング性

データ移動処理を実行できます。 能が強化されます。このような構成では、チップの動作が

よりスムーズになり、パフォーマンスが向上します。

4

RAM Amount available Suggested usage ECC Comment

RAM A 32 KB For critical data Yes Split into 4 x 8 KB sub banks

RAM B 32 KB Data Optional

RAM C 32 KB Data Optional

RAM D 64 KB Data Optional

RAM E 64 KB Data Optional

RAM F 64 KB Data Optional

RAM G 64 KB Data No RAM G and H are used to extend ECC to RAM banks B-F

RAM H 32 KB Data No and RAM X on selectedd MCX N variants

RAM X 96 KB Code Optional

MCX N94x RAMの構成概要

RAMAは最大32 KBを使用可能で、主に重要なデータに使 FlexSPIコントローラ

用されます。このRAMバンクは、8 KBずつ4つのサブバン

クに分割されており、それぞれが独立して制御できる電源 MCX N94xには、以下のタイプの外部メモリや FPGAへの

スイッチを備えています。VBAT電源領域に32 KBのバン 接続をサポートするために、 FlexSPIコントローラが組み

クが配置されていることにより、開発者はディープ・ 込まれています。

パワーダウン・モードとVBAT電源モードでRAMの容量を

最大32 KBまで柔軟に確保できます。RAMAの8 KBの各バ • シリアルNORフラッシュ

ンクは、1ビット訂正と2ビット検出機能を備えたECCを、 • シリアルNANDフラッシュ

使用可能なメモリ・サイズを縮小することなくサポートで

きます。 • HyperBusデバイス(Hyperフラッシュ/RAM)

• シリアルRAMデバイス(pSRAMなど)

RAMバンクB~Gは、システムのRAM電源領域に電力が供

給されたときにオンになります。これらのブロックには独 • XCCELAデバイス

立した電源スイッチがあり、スイッチのオン/オフや状態維 • FPGAデバイス

持モードへの移行によってエネルギーを節約できます。

フラッシュ・アクセス・モードを設定することで、以下の構

SRAMのパフォーマンス:初期の測定結果によると、 成をサポートできます。

最適化された設定では、150 MHzで動作するプライマリ

Cortex-M33コアで、SRAM Xからコードを実行し、 • シングル、デュアル、クアッド、オクタル

他のSRAMバンクにデータをロードした場合、 • シングルまたはダブル・データ・レート・タイミング

4.12 Coremark MHzに達することが予想されます。

• 個別モードとパラレル・モード

内部フラッシュ:MCX N94xには、合計で最大2 MBの

フラッシュ・メモリが組み込まれています。フラッシュ・ FlexSPIコントローラには独立したAおよびBポートがあり、

スーパーセットでは、メモリが2つの1 MBメモリ・ブロッ 最大4つの外部シリアル・フラッシュ・メモリへの接続に使

クに分割されているため、開発者はRead-While-Write機 用できます。FlexSPIインターフェースにより、 execute-

能とデュアル・イメージ・アプリケーションを実装できま in-Place (XIP) やオンザフライでの暗号化、復号化、認証が

す。フラッシュ・メモリ・コントローラは、フラッシュへ 可能です。また、16 KBのキャッシュも搭載され、

のアクセスを管理しており、フラッシュ・アクセスの CACHE64 AHBキャッシュ・コントローラによって管理され

パフォーマンスを最適化するためにバッファとキャッシュ ています。キャッシュ・コントローラ・モジュールにより、

が組み込まれています。フラッシュ・メモリには、すべて アドレス領域ごとに異なるキャッシング・ポリシーを適用で

のコアとバス・マスタ(uSDHCを除く)からアクセスでき きます。FlexSPIのメモリとキャッシュには、システムの他

ます。 のコアやバス・リーダーからアクセスできます。

内部フラッシュのパフォーマンス:初期の測定結果による FlexSPIのパフォーマンス:初期の測定結果によると、

と、最適化された設定では、キャッシュを有効にして 最適化された設定では、150 MHzで動作するプライマ

150 MHzで動作するプライマリ・コアからコードを リ・コアで、FlexSPIインターフェースからコードを

実行し、SRAMでデータの格納とロードを行った場合、 実行し、SRAMでデータの格納とロードを行った場合、

4.12 Coremark MHzに達することが予想されます。 4.12 Coremark MHzに達することが予想されます。

5

CACHE64メモリ・コントローラには、以下の複数の 電力設定の評価とテスト:MCUXpresso SDKには、さま

キャッシュとバッファが含まれています。 ざまな電力モードの切り替え方法を示すサンプルが用意さ

• プライマリ・コア上のコード・バスに密結合された れています。また、NXP評価ボードも、MCX N94xへのさ

16 KBの低消費電力キャッシュ まざまな給電方法をサポートしています。

• 任意のバス・リーダーから外部シリアル・メモリへの MCX Nシリーズのハードウェア・セーフティ機能:

キャッシュ・アクセスを可能にするためFlexSPIサブシス MCX Nシリーズには、開発者がシステム・レベルの安全認

テムに組み込まれた16 KBのキャッシュ 証を取得するのに役立つ、以下のような追加のハードウェ

ア機能が組み込まれています。

• フラッシュ・メモリ・コントローラ上の64バイトの

キャッシュ • デュアルコア:このアーキテクチャによって開発できる

セーフティ・コンセプトでは、第2のコアをメイン・

• フラッシュ読み取りを高速化するフラッシュ・メモリ・

コントローラ上の128ビットのプリフェッチ・バッファ アプリケーションから分離されたアプリケーションとし

て認定できます。

パワー・マネジメント • 誤り訂正符号を備えたSRAM:MCX Nシリーズには、 1

ビット検出および2ビット訂正機能を実現する、内蔵の

MCX Nシリーズは、柔軟なパワー・マネジメントおよびク ECCハードウェアが採用されています。開発者はRAMを

ロッキング・アーキテクチャを備えているため、開発者は 設定することでECCを有効化または無効化できます。

電力効率、サイズ、コスト、パフォーマンスを最適なバラ MCX Nシリーズのデバイス上の内部フラッシュには、最

ンスに保つことができます。 初からECCサポートが組み込まれています。

電源:MCX N94xには、いくつかの電源領域があります。 • エラー注入モジュール (EIM):内部メモリの診断率を

指定することにより、EIMはRAM読み取りデータ用の

• USB - USB PHY ECCやパリティ・ビットなど、システムの

• Analog - アナログ・ブロックのすべてのアナログ部分 エラーチェック・メカニズムに対して人為的にエラーを

• Core_Main - デジタル回路 発生させることができます。

• Core_Wake - デジタル回路/パワーダウン・ • エラー報告モジュール (ERM):誤り訂正符号 (ECC) や

ウェイクアップ・ペリフェラル パリティに関連するメモリ・エラー・イベントの発生時

に、情報の提供(およびオプションで割込み通知)を行

• System - 電源回路、ウェイクアップ・ユニット、 います。

クロック

• 巡回冗長性チェック (CRC):プログラマブルな多項式

• VDD - ポート0/1、フラッシュ、CMP、TSI によってエラー検出のための16ビットまたは32ビット

• VDDx - I/O CRCコードを生成します。

• VBAT - RTCサブシステム、RAMA、ポート5 I/O • 割込みモニタ (INTM):割込み要求に対する応答のレイ

MCX N94xには、DC/DCコンバータと低ドロップアウト テンシを監視するメカニズムを提供します。これにより、

(LDO) レギュレータが組み込まれており、開発者はどちら そのような重要な割込みの実行が想定時間内に処理され

かを使用してコア電源を生成できます。幅広い電力モード るようになり、デバイスの信頼性が向上します。

により、パフォーマンスと機能のレベルをスケーリングで • コード・ウォッチドッグ:コード実行フローにおける

きます。MCX N94xへの給電方法には、以下のようなもの 予期しない変化(誤り)を検出することにより、ソフト

があります。 ウェアの完全性を保護します。

• デバイスへの1.8 V~3.6 Vの単一電源で、すべての領域 • 外部ウォッチドッグ・モニタ:外部回路とMCUソフト

に電力を供給(最も費用対効果に優れた方法)。 ウェア・フローを監視し、MCUのCPUとペリフェラルを

• 高電圧(通常は3.3 V)とそれより リセットする内部ウォッチドッグへのバックアップ・メ

低い電圧(通常は1.8 V)を供給するデュアル電源。 カニズムを提供します。

• 外部PMICを利用すれば、システム、VBAT領域、 • ウィンドウ・ウォッチドッグ・タイマ:プログラマブル

I/Oポート2および3用の電源を個別に管理する効率的な なタイムアウトに基づきMCUをリセットするかコードの

設計を実現できます。 実行に割り込むことで、誤りのある実行を阻止します。

高度な消費電力の最適化:MCX N94xの消費電力は、各種 • 周波数測定ユニット:オンチップおよびオフチップ・ク

の高度な手法で最適化できます。たとえば、システムDMA ロック向けの高精度周波数測定機能を提供するほか、ク

(eDMA) を使用した部分的ウェイクアップのサポート、レ ロックが範囲外の場合は割込みを生成できます。

ギュレータでのドライブ能力の制御、さまざまなペリフェ

ラルやメモリでの電力およびクロック・ゲーティングなど

の手法があります。

6

Page7

MCX Nシリーズのエッジ・デバイス向け セキュリティ機能

• システム・クロック・モニタ:外部ソースからの EdgeLockセキュア・エンクレーブは、NIST P-256での

全クロック消失を検出し、リセットを生成します。 ECC暗号化処理、対称暗号化 (AES 128/192/256)

• 電圧検出:MCX NシリーズのMCUには、低電圧検出と高 (HMAC/CMAC認証)、SHA2-224/256/384/512のほ

電圧検出が組み込まれており、それらのイベントが検出 か、RFC5869準拠のHKDF、NIST 800-108準拠の

された場合に割込みとリセットの生成を行います。 CKDF、RFC3394の鍵ラップ/ラップ解除、

NIST 800-90A準拠のDRBGなどの鍵導出関数 (KDF)

• セキュアAHBコントローラ:非セキュアなソフトウェア 規格をサポートしています。EdgeLockセキュア・エン

による意図しない変更や悪意のある変更を防止します。 クレーブは、128ビット x 20スロットで構成される専

開発者はセキュアAHBコントローラを使用して、すべて 用のRAMに鍵ストアも備えています。このエンクレーブ

のペリフェラルへのアクセスのセキュア・レベルを定義 には、デバイス認証、プラットフォームの完全性(ソフ

できます。セキュアAHBは、デフォルトですべてのペリ トウェアの検証、ソフトウェアの更新、認証済みデバッ

フェラルに最高レベルのセキュアな特権アクセスを設定 グ)、オンザフライのフラッシュ暗号化/復号化/認証、

します。 セキュアな接続用の鍵が格納されます。このエンクレー

• ADコンバータ (ADC):ソフトウェア機能やハード ブには、セキュアな鍵ストレージを利用可能な任意のス

ウェア機能を組み合わせて、ADCのセルフ・キャリブ トレージへと拡張できる、組込みの鍵ラッピング関数が

レーションおよびセルフ・テスト・ルーチンをシステム 含まれています。鍵導出関数がいくつか用意されている

に組み込むことができます。そうすることでADCの信頼 ため、マスタ鍵から複数の使用鍵を作成できます。また、

性の高い動作を確保でき、システム全体の信頼性も高ま このエンクレーブには鍵生成関数も含まれており、

ります。 Over-The-Airでの鍵管理のためにNXP EdgeLock 2GO

サービス・プラットフォームへのセキュアな接続を行い

MCX Nシリーズのエッジ・デバイス向け ます。

セキュリティ機能

• EdgeLock公開鍵暗号化 (PKC) アクセラレータ:PKC

セキュリティは現在のエッジ・デバイス製品にとって必須 アクセラレータは、ECCおよびRSAアルゴリズムの演算

の要素であり、OEM/ODMの顧客や多数の市場にわたるエ 高速化をサポートしています。

ンドユーザーの信頼を得るための鍵となる差別化要因でもあ • ワンタイム・プログラマブル・コントローラ (OTPC):

ります。政府は米国トラスト・マークや欧州サイバー・レジ

リエンス法案などの重要な規格や規制を施行することによ OTPCは、FUSEコンテンツのロードと保管をサポート

り、製品の設計、製造、運用におけるセキュリティのベス する内蔵の4 KBのヒューズを制御します。

ト・プラクティスを強化しています。 • PRINCE暗号化/復号化:PRINCE暗号化アルゴリズム

により、内部や外部のフラッシュ・メモリに格納されて

セーフティとセキュリティは密接に関連しており、エッ いるコンテンツの機密性が確保されます。さらに、外部

ジ・デバイスの安全性を確保するには、悪意のある改ざん、 フラッシュのオンザフライ認証により、実行時のコード

妨害、操作から保護されていなければなりません。それを 保護が保証され、TOCTOU(データのチェック時と使用

可能にするため、MCX Nシリーズはセキュア・バイ・デザ 時の差異)による攻撃を防止できます。

イン手法に基づき開発されています。組込みの高度なセキ

ュリティ機能には、信頼されていない工場でのセキュア・ • 侵入および改ざん応答コントローラ (ITRC):ITRCで

マニュファクチュアリングとIP盗難防止、セキュアなデバ は、オンチップ・セキュリティ・センサで検出された侵

イス・ブートおよびデバッグ・アクセスによるデバイスの 入イベントへの応答アクションを設定するメカニズムを

完全性の保護、リモート・サービスへのデバイス認証、セ 提供します。

キュアな接続、セキュアなデバイス・ライフサイクル管理 • デジタル改ざん検出:この機能は、外部のデジタルI/O

などがあります。 ピンとその状態を監視し、改ざんが検出された場合にア

MCXポートフォリオで最も高度な製品であるMCX Nシリー ラームを生成します。

ズのMCUは、以下のセキュリティ機能を備えています。 • デジタルおよびアナログ・グリッチ検出:これらの検出

• EdgeLock®セキュア・エンクレーブ、コア・プロファイ 器は、電源ラインに接続され、デバイス上でローカルな

ル:他のMCU機能から物理的に分離されている 攻撃が発生していることを示す可能性のあるグリッチを

EdgeLockセキュア・エンクレーブは、独自の最適化され 検出します。

たCPUコア、ROMおよびRAMを活用し、共有リソースを • メモリ・ブロック・チェッカ (MBC):MBCは、

使用する信頼済み実行環境に特有の攻撃を防ぐ、専用の オンチップ・フラッシュをターゲットとするシステム・

セキュリティ・ユニットです。軽量で制約のあるデバイ • バス上での読み取り、書き込み、実行処理のアクセスを

ス向けに最適化され、MCX NシリーズのMCUに組み込ま 制御します。さらに、セクタ・レベルで一時的な分離を

れているEdgeLockセキュア・エンクレーブは、真性乱数 行えるようにスティッキ・ロッキング・メカニズムが組

ジェネレータ (TRNG)、暗号化サービス、セキュアな み込まれています。

鍵ストア、デバイス固有のID、デバイス認証を含むコア

機能プロファイルを備え、セキュアな接続用にトランス

ポート層セキュリティ (TLS) をサポートしています。

7

• 高度な高性能バス (AHB) セキュア・コントローラ:こ またNXPでは、OEMが委託製造業者とともに生産プロセスを

のコントローラにより、システム・レベルでセキュアな 管理できるように、Device HSM Trust Provisioningもサポー

トラステッド・エグゼキューションをサポートするため トしています。セキュア・プロビジョニング・ツールとMCX

の、セキュアAHBバスを使用した2層目の保護が実装され 評価/開発ボードを利用することで、製造プロセス中に、OEM

ています。 のソフトウェアIPと秘密鍵をシールして純正NXPデバイスに

• コード・ウォッチドッグ:このウォッチドッグは、コー 安全に転送することができるため、エンド・デバイスのセ

ド実行における予期しない変化(誤り)を検出できるた キュリティをそのライフサイクルの開始時点で強化できま

め、ソフトウェアの完全性の保護に役立ちます。 す。

• Arm TrustZone® for Cortex-M:このArmセキュリ EdgeLock Assuranceプログラム:MCX Nシリーズは、

ティ機能は、同じコア上のソフトウェア・パーティショ NXP EdgeLock Assuranceプログラムの対象となっていま

ンを交互に実行することでソフトウェアの分離を行い、 す。EdgeLock Assuranceのロゴが付いた製品はすべて、実

ペリフェラルとメモリへのアクセスを制限します。 績あるセキュリティ・プロセスに従って構築され、セキュリ

ティの業界規格(ISO 27001やISO/SAE 21434、 IEC

• セキュアなID:128ビットのUniversal Unique 62443など)を満たすように設計されており、エンドツーエ

Identifier(RFC4122バージョン5仕様準拠のUUID)、 ンドのセキュリティを実現する広範なパートナー・エコシス

256ビットのCompound Device Identifier(TCGグルー テムによってサポートされています。

プのDICE仕様準拠のCDI)

メーカーはEdgeLock Assuranceに準拠することで、データ

• 不変ROMによるプラットフォーム・セキュリティ の保護、データ・プライバシー、責任あるデータ処理に対す

– ライフサイクル管理 るNXPの取り組みに基づき、安心して設計を進めることがで

きます。

– セキュアなブート:不変の信頼の基点を提供するROM

上のセキュア・ブート・ファームウェア MCX N94xのコネクティビティ

– セキュアなデバッグ:証明書ベースのデバッグ認証メ

カニズム 統合されたコネクティビティIP:MCX N94x MCUは、

– セキュアなアップデート (ROM API):真正性の保護 コネクテッド・エッジ上で通信やインターフェースを管理す

(ECDSA署名)と機密性の保護(AES暗号化)を備え るホスト・プロセッサに隣接して動作し、コネクティビティ

たファームウェア・アップデート・カプセルをサポー 機能を実現します。MCX Nシリーズには、ペリフェラル間、

ト プロセッサ間、または外部との接続用の標準シリアル・イン

ターフェース、USB(USBフルスピード x 1、 USBハイス

– セキュア・マニュファクチュアリング:ゼロトラス ピード x 1)、UART、SPI、I2C、I3C、および外付けワイヤ

ト・ファクトリでのソフトウェアIPの保護 (Device レス・モジュール用のSDIOインターフェースが組み込まれて

HSM) います。開発者は、MCXデバイスとホスト・プロセッサや

MCX Nシリーズのセキュリティ機能の活用:MCUXpresso FPGAとの接続にFlexSPI上のHyberbusインターフェースを

SDKには、すべての主要セキュリティIPブロックを構成 活用できます。

するための低レベル・ドライバと、サンプル・アプリケー MCX NシリーズのFlexIOモジュールには、タイマ、シフ

ションが用意されています。MCUXpresso SECセキュア・ タ、レジスタが搭載され、割込みやアナログおよびデジタル

プロビジョニング・ツールを使用すれば、証明書と鍵の管 I/Oとともに使用されます。このモジュールを活用すること

理、セキュアなイメージの準備、デバイスのプロビジョニ で、標準および独自のシリアル/パラレル通信プロト

ングおよびプログラミングを通じ、MCX NシリーズのMCU

をセキュアにプロビジョニングできます。このツールには、 コル(LCDやカメラ・インターフェースを含む)を幅広く

MCX Nシリーズのデバイス上で起動可能な実行可能ファイ エミュレートできます。

ルを簡単に生成およびプロビジョニングできる、GUIベー 10/100 Mbpsのスループットをサポートする内蔵のイー

スのインターフェースがあります。既存のセキュリティ・ サネットIEEE 802.3-2008メディア・アクセス・コント

イネーブルメント・ユーティリティをベースにしたこの ローラ (MAC) は、パフォーマンスとスループットの最適

ツールには、ROM機能によって得られる幅広いプログラミン 化のためにDMAもサポートしています。また、メディア・

グ・インターフェースが活用されています。 MCUXpresso アクセス・コントローラ (MAC) はIEEE 1588タイムスタ

SECツールから生成されるスクリプトを変更することで、ユー ンプ機能も備え、エネルギー効率に優れたイーサネット・

ザーがセキュア・プロビジョニングのフローをカスタマイズで モードとパワー・マネジメントをサポートしているため、

きます。(Secure Provisioning SDKとして知られてい 低消費電力モードでの動作とウェイクアップを効率的に行

る)SECツールの基盤となるコマンドライン・ユーティリティ えます。

を使用することで、さらに高度なカスタマイズも可能です。こ

れらのユーティリティは、そのようなワークフローの開発を行 2つの内蔵CANコントローラは、CAN2.0 Bプロトコルと

えるようにソース形式で提供されています。 CANフレキシブル・データ・レート (CAN FD) プロトコ

ルに準拠し、工場、ビル、またはアフターマーケットの車

載アプリケーションで、既存のCANネットワークに簡単に

統合できます。

8

Page9

MCX N94x MCUXpresso開発者エクスペリエンス、柔軟なプロトタイピングと開発、MCX N94x MCUのまとめ

MCX Nシリーズのコネクティビティ・

ブロックの活用:MCX Nシリーズのコネ

クティビティ・ブロックは、スマート

ホーム、ビルディング・オートメーショ

ン、ファクトリ・オートメーションの各

アプリケーションの新たな波に対応でき

ます。MCUXpresso SDKには、イーサ

ネット、CAN、Wi-Fi、Bluetooth Low

Energy、超広帯域無線(UWB:Ultra-

Wideband)、Matterなどの有線および

無線プロトコル向けに、ドライバ、ミド

ルウェア、プロジェクトが組み込まれて

います。MCUXpresso SDKやZephyrプ

ロジェクトを通じてTCP/IPスタック・

オプションを利用できるほか、

Embedded System Academy (EmSA) FRDM-MCXN947 FRDM開発ボード

などのNXPパートナーから、評価スタッ

クとフル・バージョンのCAN/CAN-FD 柔軟なプロトタイピングと開発

Openスタックが提供されています。

NXPでは、MCX Nシリーズの迅速なプロトタイピングのためのプラットフォーム

MCX N94x MCUXpresso開発者エ として、低コストのFRDMプラットフォームとフル機能のEVKの両方を提供してい

クスペリエンス ます。

NXPは、MCX N94xの評価と製品開発を FRDM開発ボードは、標準のフォーム・ファクタで提供され、MCU I/Oへの簡単

効率化するために、MCUXpresso開発者 なアクセスを可能にするヘッダ、オンボードMCU-Linkデバッガ、USB-Cケーブル

エクスペリエンスを通じて、充実した を備えています。フル機能の評価キットには、I/Oおよびインターフェースへの拡

ハードウェアおよびソフトウェア・エコ 張アクセス、Wi-Fi拡張機能のほか、電力測定などの追加のMCU-Link機能が含ま

システムを構築してきました。 れます。

MCUXpresso SDKには、最終製品の開

発に必要なすべてのドライバ、ライブラ NXPのGitHubでもアプリケーション・サンプルへのアクセスを提供しており、ア

リ、ミドルウェアを含む事前テスト済み プリケーション・コード・ハブ (ACH) ポータルを使用してアクセスできます。

のボードと製品サポート・パッケージの MCUXpresso IDE(バージョン11.9.0以降)とMCUXpresso for VS Codeには、

ほか、製品評価を迅速化するプロジェク ACHブラウジングが組み込まれているため、使用可能なデモやサンプルを簡単に

ト・サンプルが用意されています。この 検索し、デバイス、アプリケーション・テクノロジ、ペリフェラル/機能でフィル

SDKには、MCUXpresso for Visual タリングしてから、使用するプロジェクトを直接ロードすることができます。

Studio Code、MCUXpresso IDE、IAR 拡張ボード・ハブ (EBH) は、NXPのSDK Builderサイトを拡張したもので、選択

Embedded Workbench、Keil MDK向 した評価ボードの機能を拡張するために、NXPやパートナーのアドオン・ボード

けのプロジェクトのほか、シンプルなデ を幅広い選択肢から選ぶことができます。このハブには、必要なものをすばやく

バイス・ピンおよびクロック構成とペリ 見つけて、使用可能なサポート・ソフトウェアを特定できる、直観的なフィルタ

フェラル・ドライバの初期化に使用でき リング機能があります。開発者は手持ちのボードをさまざまな種類のシールドと

るMCUXpresso構成ツールも含まれてい 組み合わせて評価し、特定のユース・ケースやアプリケーション向けに迅速なプ

ます。また、開発者は豊富なサード・ ロトタイピングを行うことができます。

パーティ製ハードウェアおよびソフト

ウェア・ツールも利用できます。 MCX N94x MCUのまとめ

MCUXpresso SDKには、ベア・メタ

ル・ビルドとFreeRTOSのサポートが含 MCX N94x MCUは、インテリジェントなコネクテッド・エッジベースのアプリ

まれ、MQX RTOSも個別に利用できま ケーションの大幅な増加という、進行中のメガトレンドに対応できるよう設計さ

す。NXPはZephyr Foundationの創設メ れています。センサの数とエッジで収集、処理されるデータの量は、今後数年に

ンバーであり、同プロジェクトに含まれ わたって飛躍的に拡大していくことになります。そうしたトレンドに対応するた

るすべてのMCX NシリーズのMCUに対 めにNXPが設計したMCX N94xは、複数のコアとアクセラレータを内蔵しており、

して全面的なサポートを提供する予定で 複雑なML、センシング、コネクティビティを処理し、シングルチップ・ソリュー

す。 ションでアプリケーションを制御しながら、拡大の一途をたどるパフォーマンス

需要を優れた安全性、セキュリティ、スペース効率、電力効率で満たすことがで

きます。開発者はMCX N94x MCUの処理能力および機能を活かし、NXPとパート

ナーによる包括的な開発エコシステムを活用することで、製品の市場投入までの

nxp.jp/MCXN94x 期間を短縮できます。

NXPおよびNXPのロゴは、NXP B.V.の商標です。その他すべての製品名、サービス名は、それぞれの所有者に帰属します。© 2024 NXP B.V.

ドキュメント番号:MCXN94XWP REV 0