プログラマブル ロジック:

車載システムのアクセラレーション

はじめに

車載システムは自動運転機能を装備するため、ますます高度な技術を必要としています。自動運転機能は、完全自動運転から、ドライバー

と運転権限をシェアする権限移譲型自動運転まで、さまざまな機能を網羅する複雑な技術分野です。この、自動運転機能を分類するため、

米国自動車技術会(SAE)では、次段階の基準を定めています。

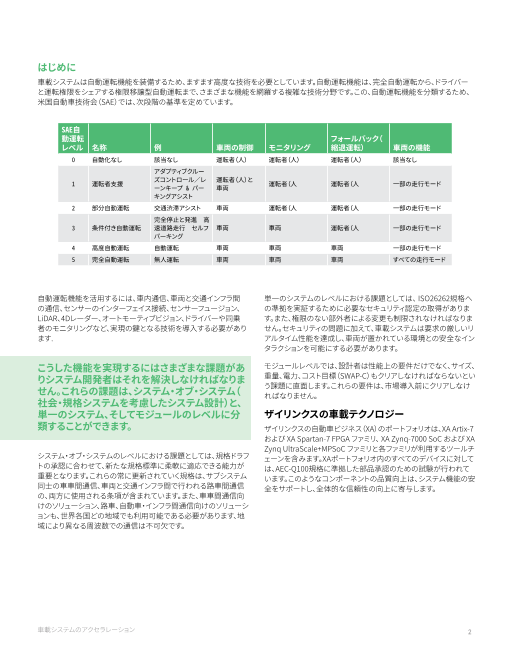

SAE自

動運転 フォールバック(

レベル 名称 例 車両の制御 モニタリング 縮退運転) 車両の機能

0 自動化なし 該当なし 運転者(人) 運転者(人) 運転者(人) 該当なし

アダプティブクルー

1 運転者支援

ズコントロール/レ 運転者(人)と

ーンキープ & パー 車両

運転者(人 運転者(人 一部の走行モード

キングアシスト

2 部分自動運転 交通渋滞アシスト 車両 運転者(人 運転者(人 一部の走行モード

完全停止と発進 高

3 条件付き自動運転 速道路走行 セルフ 車両 車両 運転者(人 一部の走行モード

パーキング

4 高度自動運転 自動運転 車両 車両 車両 一部の走行モード

5 完全自動運転 無人運転 車両 車両 車両 すべての走行モード

自動運転機能を活用するには、車内通信、車両と交通インフラ間 単一のシステムのレベルにおける課題としては、 ISO26262規格へ

の通信、センサーのインターフェイス接続、センサーフュージョン、 の準拠を実証するために必要なセキュリティ認定の取得がありま

LiDAR、4Dレーダー、オートモーティブビジョン、ドライバーや同乗 す。また、権限のない部外者による変更も制限されなければなりま

者のモニタリングなど、実現の鍵となる技術を導入する必要があり せん。セキュリティの問題に加えて、車載システムは要求の厳しいリ

ます. アルタイム性能を達成し、車両が置かれている環境との安全なイン

タラクションを可能にする必要があります。

こうした機能を実現するにはさまざまな課題があ モジュールレベルでは、設計者は性能上の要件だけでなく、サイズ、

りシステム開発者はそれを解決しなければなりま 重量、電力、コスト目標(SWAP-C)もクリアしなければならないとい

せん。これらの課題は、システム・オブ・システム( う課題に直面します。これらの要件は、市場導入前にクリアしなければなりません。

社会・規格システムを考慮したシステム設計)と、

単一のシステム、そしてモジュールのレベルに分 ザイリンクスの車載テクノロジー

類することができます。 ザイリンクスの自動車ビジネス(XA)のポートフォリオは、XA Artix-7

および XA Spartan-7 FPGA ファミリ、 XA Zynq-7000 SoC および XA

Zynq UltraScale+MPSoC ファミリと各ファミリが利用するツールチ

システム・オブ・システムのレベルにおける課題としては、規格ドラフ ェーンを含みます。XAポートフォリオ内のすべてのデバイスに対して

トの承認に合わせて、新たな規格標準に柔軟に適応できる能力が は、AEC-Q100規格に準拠した部品承認のための試験が行われて

重要となります。これらの常に更新されていく規格は、サブシステム います。このようなコンポーネントの品質向上は、システム機能の安

同士の車車間通信、車両と交通インフラ間で行われる路車間通信 全をサポートし、全体的な信頼性の向上に寄与します。

の、両方に使用される条項が含まれています。また、車車間通信向

けのソリューション、路車、自動車・インフラ間通信向けのソリューシ

ョンも、世界各国どの地域でも利用可能である必要があります、地

域により異なる周波数での通信は不可欠です。

車載システムのアクセラレーション 2

ISO26262規格で定められているとおり、自動車安全水準(Automotive Safety Integrity Level、ASIL)による認証を可能にするため、ザ

イリンクスはさまざまな認定ツールチェーンとソフトウェアツールを用意しております。

電力効率とコスト効率に優れたソリューションでありながらも要件を満たすには、車載システムに適したデバイスを選択する必要があり

ます。XA Artix-7 および XA Spartan-7 ファミリのデバイスは、従来のFPGAベースからのアプローチを提供し、シーケンシャル処理が必要

な場合にはソフトコア・プロセッサを実装することが可能です。

要件がさらに厳しい性能が求められる場合は、ザイリンクス XA Zynq UltraScale + MPSoC や XA Zynq-7000 ヘテロジニアス SoC が、

処理システム(PS)とプログラマブルロジック(PL)の優れた組み合わせを提供します。

ザイリンクス XA Zynq UltraScale + MPSoC デバイスの特徴: ザイリンクス XA Zynq SoC デバイスの特徴:

– 最 大1.2GH(z fmax)で動作可能なクアッドコア 64 bitの ARM – 最大667MHz FMAXで動作できる32 ビット Dual core Arm

Cortex-A53 プロセッサと、最大500MH(z fmax)で動作可能な Cortex-A9 プロセッサを搭載したプロセッシングシステ

デュアル 32 bit ロックステップ ARM Cortex-R5 プロセッサを ム:PS部

内蔵したリアルタイム処理ユニットを搭載したプロセッシング

システム:PS部 – 最大464MH(z Fmax)で動作でき、設定が可能なロジック

ブロック、ブロック RAM 、およびDSPエレメントを内蔵する

– 最 大645MH(z fmax)で動作でき、設定が可能なロジックブロ 28nmアーキテクチャによるプログラマブル・ロジック:PL部

ック、ブロック RAM 、およびDSPエレメントを内蔵する16nm

UltraScale+ アーキテクチャによるプログラマブル・ロジッ

ク:PL部

Zynq UltraScale + MPSoC と Zynq-7000 によっても

たらされるPS部とPL部の密接な連携により、最新型

の車載システムの要求を満たすことができます。

FPGAソリューションも、ヘテロジニアスSoC向けソリューションも、ともに、プログラマブル・ロジックが搭載されています。このプログラマブ

ル・ロジックを使いアルゴリズムの並列処理を行うことで、アルゴリズムのレイテンシーを劇的に低下させ、確定的なアルゴリズム開発を可

能とします。プログラマブル・ロジックはまた、各種PHYとのAny-to-Anyのインターフェイスを自由う設計できるため、CPU、GPU、ASICソリュ

ーションと比べ、各種規格の変更やアップデートに柔軟に対応できます。

ザイリンクスのツールチェーン

ザイリンクスのXAデバイスの各PS, PL部の設計やコンフィギュレーションは、Vivado Design Suite を使用して開発されます。

Vivadoは統合開発環境で配置配線、シミュレーションのサポートなど、プログラム・ロジック開発において、多くの実績があります。もう一

つ、Vivadoの重要な側面として設計資産の再利用が挙げられます。これにより過去の設計資産やIPコアを使って、設計を完成させることが

容易です。Vivadoを使用することで、設計者は XA Zynq-7000 SoC や XA Zynq UltraScale-+MPSoC デバイスに搭載されるプロセッサと共

に、広範なIPカタログに登録されたIPコア群を周辺として活用することができます。

カスタムIPブロックが必要な場合は、VHDLやVerilogなどのハードウェア記述言語を使用して作成することもできます。また、Vivado Level

Synthesisにより、CまたはC++のデザインをプログラマブル・ロジック内に実装することも可能になります。

ソフトウェアソリューションの開発には、Vitisを用います。これは、Cortex-A9、A53、R5、および MicroBlaze ソフトコア・プロセッサ用のソフト

ウェアの作成を容易にする統合ソフトウェア開発用プラットフォームです。

車載システムのアクセラレーション 3

Vitisは、PetaLinux を使用した組み込みLinuxの開発をサポートす XA Zynq UltraScale + MPSoC デバイス・ファミリは、プロセッシ

ると同時に、FreeRTOSなどのリアルタイムOSもサポートします。フ ングシステム内のコンフィギュレーションセキュリティ・ユニット

レームワークが提供され、OpenAMPなどのマルチプロセッサ環境 (CSU)の機能を備えたセキュリティ機能をさらに強化し、階層型

における通信やライフサイクル・マネージメントが容易になります。 セキュリティ機能を実現します。CSUがAES 256- GCM、4096 RSAマ

ルチプライヤ、SHA-384をサポートしており、デバイスの安全な再

構成(コンフィギュレーション)が可能になりソリューションの機密

システム開発機能だけでなく、VITISは、 性、認証、堅牢性が実現します。

OPENCLを使用した高速化もサポートします

CSU暗号化エンジンのAES、RSA、SHAブロックをランタイムに使用

して、機密性、認証、堅牢性機能を実現することもできます。CSUの

OpenCLにより、APU(Application Processing Unit)の制御下で、 DMAは非常に効率的な処理を可能にします。CSUは、Rolling Key

アクセラレーション(高速化)カーネルをプログラマブル・ロジック 機能を有効にして、差動電力解析によるキー攻撃を防御するなど、

内に導入することが可能になります。これにより、アルゴリズムの キー管理を行うこともできます。

ハードウエア・アクセラレーションをソフトウエアエンジニアでも ランタイム・セキュリティ・サポートには、内蔵システムモニター

実現出来るようになります。これは、アルゴリズム内で利用される (FPGAデバイスとSoCデバイスの両方)による改ざん防止対策が

C、C++記述を高位合成でハード実装させることを意図します。ま 含まれています。これにより、デバイス電圧やダイ温度が限界を超

た、Pragma記述を使用することでアルゴリズム処理を並列処理に えた場合、警告を発信し、監視することができます。システムモニタ

展開しプログラマブル・ロジックに実装することで、パフォーマンス ーには外部接続もあり、エンクロージャレベルでの、より物理的な

を最適化することを可能としています。 不正操作防止策として使用できます。

セキュリティ 安全性

すべてのザイリンクスXAデバイスには、Advanced Encryption 自動車システムのメーカーが直面している重要な課題の1つは、

Standard( AES)に基づいて暗号化ビットストリームを使用し、デ 適切な安全性・品質規格に準拠した安全システムを実現すること

バイスを安全に再構成(コンフィギュレーション)する機能がありま です。

す。XA Zynq-7000 SoC や XA Zynq UltraScale + MPSoC のデバイ

スを利用すると、プロセッサ・システムとプログラマブル・ロジック 自動車業界においては、これは機能上の安全性に関連しており、

の組み合わせにより、セキュアな(再構成)コンフィギュレーション システムの危険性のレベルを示す ISO26262規格の自動車安全水

手法がより完全なものとなります。 準(Automotive Safety Integrity Level、ASIL)の4段階のうち、い

ずれかに準拠しなければなりません。

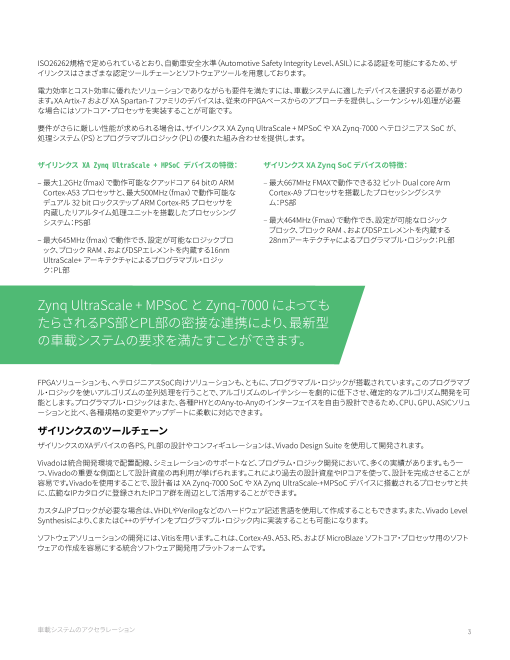

自動車

安全水準 重要度 故障率(FIT、10億時間 検出率 結果

(ASIL あたりの平均故障回数)

単一箇所における故障検

ASIL-D 最重要 FIT10未満 出率 >99% 潜在的な故障 Possible fatalities

検出率 >90% in community

単一箇所における故障検

ASIL-C FIT100未満 出率 >97% 潜在的な故障 Possible fatalities

検出率 >80%

単一箇所における故障検

ASIL-B FIT100未満 出率 >90%潜在的な故障 Possible for minor injuries

検出率 >60%

単一箇所における故障検

ASIL-A 最も低い重要度 FIT1000未満 出率 <90%潜在的な故障 Potential for minor injuries

検出率 < 60%

QM 品質管理 NA 安全性に関連しない

車載システムのアクセラレーション 4

Single point of failure(SPOF)は、単一障害によるリスクを防止す XA Zynq UltraScale + MPSoC 低電力ドメイン、リアルタイム処理

る安全設計の指標であり、Latent fault metric(LFM)は、安全設計 ユニット、および安全マニュアルは、このほど、ISO26262:2011規

によって検出できない複数箇所における故障に関する指標です。 格に基づきASIL-Cとして認証されました。

故障率FIT(Failure in Time)は、10億時間以内に発生が予測され

る装置の故障件数を表します。より重要なシステムには、より低い ASIL-Cソリューションの実装を可能にするアーキテクチャ機能に

FIT値が求められるため、設計者にとっては達成に試練を要する は、以下があります。

目標となります。

– Low power、Full power、およびプログラマブル・ロジックの3つ

システムに関するASILは、下記項目に関して危険分析を行うこと の独立したドメイン。各ドメインには、ハードウェアにフォールト

により、決定されます。 トレランスをもたらす専用電源とクロッキングを有します。

– 重大度 – ドライバーまたは同乗者が受けるおそれのある傷害 – プラットフォーム管理ユニットで、TMRブートの安全性、電源、エ

ラーを管理するプロセッサ

– 曝露確率 - 車載システムや車両が危険に曝される頻度

– Low powerドメインには、ロックステップモードつきの ARM

– 制 御可能性 – ドライバーや車両が傷害を防止するために取るこ Cortex-R5 プロセッサ

とのできる操作

– プロブラグラマブル・ロジックの分離を可能にする、メモリ・周

このため、車両に搭載されている各システムのASILリスク等級は 辺機器保護ユニット

異なります。たとえば、ブレーキ、ステアリング、エアバッグなどの

重要なシステムは、通常、ASIL-Dであり、 – Critical memoryのエラー訂正コード

一方、ヘッドライトやADASシステムなどのシステムは、通 – ロジックやメモリを内蔵したセルフテスト、エラーインジェクシ

常、ASIL-Bです。 ョン、ソフトウェアテストライブラリを含むテスト可能なアーキテ

クチャ

要求されているASILを満たす設計を実現するには、単一箇所に

おける故障および潜在的故障を検出してそのリスクを軽減でき 認証が必要な場合、 ザイリンクスの自動車用デバイスのポートフ

るよう、本格的な設計分析や故障モードの検討を行う必要があ ォリオを、ISO26262-8:2011規格に準拠して認証されたツールが

ります。 サポートします。

認証済みのツールを利用できるため、開発者は、開発期間全体を

IPコア、デバイスアーキテクチャ、およびザイリン 短縮でき、高品質かつ低コストでプロジェクトを期限に合わせて

クスWEBが提供するドキュメントサポートで、必

完了することができます。

要とされている機能安全レベルの達成できます また、安全マニュアル、ソフトウェア安全ユーザーガイド、 FMEDA

ツール、サンプル、定期的な信頼性レポートなど、認証を取得する

ために設計されたシステムおよび分析ツールもご用意しておりま

ブロック RAM のエラー検出や訂正を含む、信頼性の高い論理設 す。これらのリソースは、ザイリンクスの機能安全パッケージから

計のためのプログラマブル・ロジックのローレベル・サポートが行 入手可能です。

われます。Triple Module Redundan(t TMR)やロックステップのオ

プションのついた MicroBlazeソフトコア・プロセッサをプログラブ これらの開発ツールを、ザイリンクスの自動車用デバイスと組み

ルロジックに実装することで多様な構成を可能とします。 合わせて使用することで、開発者は、最新の自動車開発の課題に

対応することができます。

また、XADC と Sysmon を使用してデバイスの電源レールとダイ

温度を監視、閾値を超えた場合はアラームを発効させることも出

来ます。

プログラマブル・ロジック内における各機能の分離はザイリンク

スのIsolation design flow (IDF)とVivado Isolation Verifier (VIV)

を使用して実装検証できます。これにより プログラマブル・ロジッ

ク内に実装された機能の間の分離が確保されます。

車載システムのアクセラレーション 5

複数拠点間インターフェイス接続

自動運転機能を実装する核心部分となるのは、異なるモダリティを持つセンサー群、アクチュエータや多様な規格のインターフェイスとの

接続性と言えます。センサーからデータを受信すると、車両がそれに反応できるように判定処理を行う必要があります。

センサーとのインターフェイスとその処理における、重要な課題の1つとして、プロセッサはさまざまな高帯域センサーモダリティとのインタ

ーフェイス実現性が求められることが挙げられます。

これらのモダリティはすべて、異なるインターフェイス規格を備えています。一般的なソリューションでは、カメラ、レーダー、LiDARなどの広

帯域幅センター用のMIPI 、JESD204B、LVDS、GigEなどの高速インターフェイスを使用するさまざまなセンサーモダリティからデータを受信

します。また、加速度計等の低帯域センサーとのインターフェイスにはCAN、SPI、I2C、UART等の標準規格での通信とその処理が必要となり

ます。

Zynq UltraScale-+MPSoC のプロセッシングシステムやプログラマブル・ロジックは、CAN, SPI, I2C , UARTおよびギガビットEthernet等の

業界標準インターフェイスをサポートしています。

プログラマブル・ロジックが有するI/Oの柔軟性によりMIPI, LVDSやその他のGigaビット・ シリアルリンクとのダイレクト・インターフェイスが

可能です また、各種IPコアを搭載して、より高いレベルのプロトコルをプログラマブル・ロジック内に実装することができます。また、プロ

グラマブル・ロジックにプロトコルを実装することで、規格の改訂に素早く対応することができ、システムでサポートが求められる数多くのセ

ンサーの通信規格に柔軟に対応できます。また、プログラマブル・ロジックは、ハードウェア・デザインとして将来的に必要となるPHYとの接

続性を提供する可能性を持ち、真のAny to Anyインターフェイス接続を可能にしています。

画像処理の高速化

画像処理は、ナビゲーションから、ドライバーや同乗者のモニタリングにいたるまで、あまたの車載システムにおいて、その中核を担います。

通常、これらのシステムで使用されるアルゴリズムは、OpenCVなどの高レベルのフレームワークで作成されモデル化されます。

PLソリューションは、画像のパイプライン処理を論理的に構築できるため、画像処理システム

のパフォーマンスを大幅に向上させることができます。このパイプライン処理は、PLのパラレ

ル特性を活用します

OpenCVなどのフレームワークで作成された高レベルのアルゴリズム・モデルを、HDLによってすべて再作成することなく活用できるよう

にするため、ザイリンクスは、XF::OpenCVライブラリを提供いたします。Vitis統合ソフトウェア開発プラットフォームのハイレベル統合を

使用してPLに統合できるOpenCV関数のうち、一般に広く使用されているいくつかが、XF::OpenCVライブラリに含まれています。これによ

り、OpenCVを使用してハイレベルのモデリングを行うことができ、ハードウェア記述言語を延々と記述することなく、PLパイプライン内で、

同じ関数をすばやく簡単に実装できます。

車載システムのアクセラレーション 6

画像処理またはダウンストリーム処理に必要とされるH.264/H.265 がありました。ベースバンド信号は、アナログ-デジタル・コンバータ

エンコーディングまたはデコーディング処理性能をXA Zynq (ADC)およびデジタル-アナログ・コンバータ(DAC)を使用して、ア

UltraScale + MPSoC EVシリーズに搭載されたストリームのバッファ ナログ領域への変換および同領域からの変換が行われます。

リング用UltraRAMとVideo CODECユニットが提供します

ザイリンクスの Zynq UltraScale + RFSoC デバイスポートフォリオ

ニューラルネットワークの高速化 には、高性能クアッドコア ARM Cortex-A53 64 ビットプロセッサを

画像処理についで、オートメーションシステムの開発を可能にする

搭載したプロセッシングシステムだけでなく、

ための、もう1つの重要なテクノロジーが、機械学習です。たとえば、 GSPS(ギガサンプル/秒)クラスのADCやDACに加えて、アップコン

機械学習を利用して、高速道路上の物体を分類したり、ドライバー バータ、ダウンコンバータ、複雑なミキサー、インターポレーター、デ

や同乗者を監視したりモニタリングしたりすることができます。 シメーターなど、必要なサポートインフラストラクチャサポートイン

ニューラルネットワークの実装と高速化に、Vitis AI を利用可能

フラストラクチャを内蔵するプログラマブル・ロジックも含まれてい

です。Vitis AI は、プログラマ風呂ロジックを利用して、Caffe や

ます。

TensorFlow 等、広く利用されているML/AI フレームワークをア これにより、RFフロントエンドとのインターフェイスの複雑さが大幅

クセラレーションすることができます。Vitis AI は Model Zoo, AI に緩和されるだけでなく、要求される実装面積も全体的に縮小で

compiler, Optimizer, Quantizer, Profilerを提供し、システムへのデ きます。

ィープラーニング処理ユニットを実装を可能としました。

ザイリンクスの Zynq UltraScale + RFSoC の主な構成要素

ミックスドシグナル機能 は、GSPSレベルのサンプリングレートで処理可能なADCコンバータ

レーダーは、霧や豪雨など、明るさや天候条件を問わず、常に機能 とDACコンバータになります。世代によってこのサンプルレートには

する唯一のセンサー技術です。より高次のSAE自動運転レベルによ 幅があり、第1世代のADCでは2Gサンプル/秒、第3世代のデバイス

る運転を実現するため、十分に正確な情報を取得する目的で、頻繁 では5Gサンプル/秒で、4つのナイキストゾーンすべてで動作を可

に利用されるのが4次元レーダーです。 能にするRF入力帯域幅をサポートします。サンプリングDACのレー

トは、第1世代の6.5Gサンプル/秒から第2世代の10Gサンプル/

4Dレーダーにより、方位、高度、直線距離のほか、ドップラー周波数 秒まであります。このサンプリングレートと広いRF入力帯域幅の組

についても情報が得られます。ドップラー周波数を活用すれば、検 み合わせにより、RF Tx および Rx パスの複雑さが大幅に緩和され

出ターゲットの速度が決定できます。これにより、4Dレーダーは、広 ます。

い視野(100度)、細やかな空間分解能(1度)、それに長距離機能(

約300m)を備えたシステムを提供します。これが、交通渋滞時アシス 結論

ト、高速道路走行、セルフパーキングなどの機能を備えた、SAE自動 自動車の機能に対する要求が高まる中、設計者は、ザイリンクスXA

運転レベル2および3での自動運転を可能とします。 の車載デバイスやサポートツールチェーンのポートフォリオにより、

求められる性能だけでなく、必要とされる品質や機能上の安全性、

従来のレーダーソリューションでは、アップコンバージョンやダウン

また情報のセキュリティを実現することができます。

コンバージョンを行うには、RFフロントエンドにおける信号生成や

長時間の信号処理にベースバンドデジタル処理を使用する必要

車載システムのアクセラレーション 7

アヴネットについて

アヴネットは、グローバルな技術ソリューションプロバイダとして、膨大な

エコシステムを活かし、製品のライフサイクルのあらゆる段階において、

顧客へ設計、製品、マーケティング、およびサプライチェーンの知識経験を

提供しています。またアイディアをインテリジェントなソリューションに変

換し、商品化にかかる時間、コスト、そして複雑さを減らします。そして、約

100 年に亘り、世界中のお客さまおよび サプライヤーが技術の変革を実

現するために支援してきました。

アヴネットの詳細についてはこちらを参照してください。

WWW.AVNET.COM/JAPAN

著作権© 2020 アヴネット株式会社 AVNET、「Reach Further」、およびアヴネット社のロゴは、アヴネット Avnet

株式会社の登録商標です。その他のすべてのブランドも、各所有者の財産です。 avnet.com/japan