1/32ページ

ダウンロード(11.6Mb)

ザイリンクスのテクノロジーとエコシステムがその課題の克服にどのように役立つかを解説

自動車ソリューションは、電子システムに依拠して車両に自律機能を実装します。この能力により電子システムはリアルタイム処理用件や、さまざまな高帯域幅・低帯域幅センサー全てのインターフェイスを実現することが可能となります。自律機能は、不正なアクセスや変更を防止する確実かつ安全な実装を提供し、安全な操作と(性能劣化が余儀なくされた場合でも、その劣化を出来るかぎり緩やかにとどめる)グレースフルデグラデーションを保証します。自律走行車の領域では、次のキーとなるシステムを開発する必要があります。

- 自律的視覚システム

- 自動車用レーダー

- センサーの集約と処理

- 安全認証

- 搭乗者モニタリング

- 車両間およびインフラストラクチャ間通信

このeBOOKでは、エンジニアがこれらの重要なシステムを開発する際に直面するさまざまな課題を探り、ザイリンクスのテクノロジーとエコシステムがその課題の克服にどのように役立つかを解説します。

◆目次

車載用ビジョンシステム

ADAS用RADAR

車載アプリケーションでの集約、融合、アクセラレーション

自動車の機能安全

搭乗者モニタリング

VehicletoEverything(V2X)通信

◆詳細はカタログをダウンロードしご覧いただくか、お気軽にお問い合わせ下さい。

このカタログについて

| ドキュメント名 | 自律走行車のユースケーストップ6 |

|---|---|

| ドキュメント種別 | ホワイトペーパー |

| ファイルサイズ | 11.6Mb |

| 登録カテゴリ | |

| 取り扱い企業 | アヴネット株式会社 (この企業の取り扱いカタログ一覧) |

この企業の関連カタログ

このカタログの内容

Page1

自律走行車のユースケーストップ6

Page2

自律走行車のユースケーストップ6

自動車ソリューションは、電子システムに依拠して車両に自律機能を実装します。この能

力により電子システムはリアルタイム処理用件や、さまざまな高帯域幅・低帯域幅センサ

ー全てのインターフェイスを実現することが可能となります。自律機能は、不正なアクセ

スや変更を防止する確実かつ安全な実装を提供し、安全な操作と(性能劣化が余儀なく

された場合でも、その劣化を出来るかぎり緩やかにとどめる)グレースフルデグラデーシ

ョンを保証します。

自律走行車の領域では、次のキーとなるシステムを開発する必要があります。

- 自律的視覚システム

- 自動車用レーダー

- センサーの集約と処理

- 安全認証

- 搭乗者モニタリング

- 車両間およびインフラストラクチャ間通信

このeBOOKでは、エンジニアがこれらの重要なシステムを開発する際に直面するさまざ

まな課題を探り、ザイリンクスのテクノロジーとエコシステムがその課題の克服にどのよ

うに役立つかを解説します。

目次

車載用ビジョンシステム . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

ADAS 用 RADAR . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

車載アプリケーションでの集約、融合、アクセラレーション . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

自動車の機能安全 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

搭乗者モニタリング . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Vehicle to Everything(V2X)通信 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

アヴネットの詳細についてはこちらを参照し

てください。

www.avnet.com/japan

2

Page3

はじめに

今日の自動車の安全性と技術革新は、かつて18世紀から19世紀に最初の自動車が製造され、数年で急速な進化と利用が進んだ時代

のような、新たなる変革の時代を迎えています。

今日の自律走行車は、四輪車両に構築された複雑なシステムであり、複数機能がさまざまな自律レベルで動作し、キャビン内外でAIを

包括して統合されています。 四方に設置されたカメラとセンサーは、膨大な量のデータ生成と処理を同時に行います。 しかし、この

複雑さが大きな課題をもたらします。 これらのシステムは、リアルタイム性能および信頼性を備えなければならず、相互に通信する必

要があるからです。

ザイリンクスのオートモーティブグレード(XA)デバイスは、現在そして将来の自律走行車が必要とするインターフェイス、処理性能、安

全性、低遅延、および決定性の課題に対処します。例えば、このeBOOKで取り上げられているヘテロジニアス・システムオンチップXA

Zynq UltraScale + MPSoC は、プロセッシングシステム(PS)とプログラマブルロジック(PL)を提供し、複数機能間のインターフェイス接

続や、単一のデバイスによる機械学習推論など複数の機能を高速化するポテンシャルを備えています。

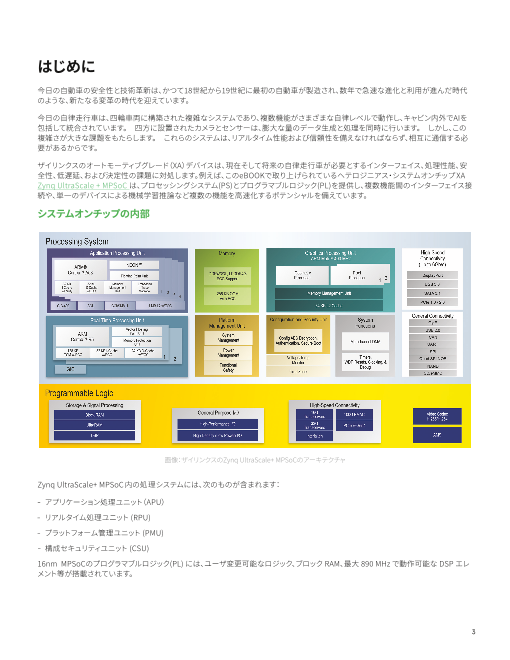

システムオンチップの内部

画像:ザイリンクスのZynq UltraScale+ MPSoCのアーキテクチャ

Zynq UltraScale+ MPSoC内の処理システムには、次のものが含まれます:

- アプリケーション処理ユニット(APU)

- リアルタイム処理ユニット (RPU)

- プラットフォーム管理ユニット (PMU)

- 構成セキュリティユニット (CSU)

16nm MPSoCのプログラマブルロジック(PL) には、ユーザ変更可能なロジック、ブロック RAM、最大 890 MHz で動作可能な DSP エレ

メント等が搭載されています。

3

Page4

ANY-TO-ANYインターフェイス接続

ザイリンクスのSoCsは、プロセッシングシステム(PS)からアクセス可能なさまざまなイン 自動車設計者によるシフト実現

ターフェイスを開発者に提供します。 これらは、通信やセンサーに使用されるSPI, I2C, の手助け

UARTなどの低速・低帯域幅のインターフェイスから、高速・高帯域のインターフェイスの

USB、SATA、PCIe等までさまざまです。 更にプログラマブルロジックと搭載するPHY(物 開発ツール、IPライブラリ、設計フレームワ

理層)を組み合わせて、オーダーメイド、レガシー、そして急速に変化する新たな業界標準 ークに至る堅牢なエコシステムとザイリン

を簡単に実装することが出来る、『Any-to-Anyインターフェイス接続』を提供します。 クスのプログラマブルテクノロジーの幅広

いポートフォリオは、日々進化する自律走

SWAP-C の削減 行車の開発環境に適応します。

プログラマブルシステム(PS)とプログラマブルロジック(PL)の緊密な統合により、設計者

は自動車システムに求められるサイズ、重量、電力、コスト(SWaP-C)の厳しい要件を満

たすソリューションを実現できます。この統合により、必要デバイス点数を削減、基板面積

が削減可能となり、更にデバイス間伝送が削減されることで消費電力低減にも寄与する

ことが出来ます。

ザイリンクスのオートモーティブグレードデバイス

は、部品認証のためのAEC-Q100規格要件に対応。

このように、コンポーネント品質向上により、システ

ム全体の信頼性が増すことで、高いレベルの機能

安全が実践可能です。

4

Page5

自動車アプリケーション用ビジョンシステム

はじめに

自律走行機能では、車両がその周囲環境を確実に把握する必要があります。周囲環境認

識を実現する最も一般的な手法の1つは、組み込みビジョンシステムの利用です。 安全性およびセキュリティ

これらビジョンシステムにより、車両のシステムは周囲を認識するだけでなく、取得画像 車載ビジョンシステムはその特性上、安全

処理を行う事で人、車両、物体を検出および分類できます。これら機能は、交通渋滞アシ 性とセキュリティの観点からの考慮が欠か

スト、セルフパーキング、高速道路運転の停止/開始、SAEレベルの向上など、多くの自律 せません。これは、ISO 26262 の安全基準

運転の基礎となります。 との整合性を意味することが多いため、システムのアーキテクチャでは安全性を優先

アーキテクチャの機能と考慮事項 する必要があります。

普通の車両アーキテクチャは、カメラ処理モジュールに接続された複数のカメラを使用し

ています。このカメラ処理モジュールは、機械学習推論などの高度なアルゴリズムを行う

前に、カメラ制御、画像キャプチャ、および前処理を行います。

次に、これらの高度なアルゴリズム(推論)処理の結果は適切な車両システムに伝達さ

れ、アクションが行われます。通常、画像から抽出されたデータは、車両の中央処理システ

ムに伝えられ、車両制御に影響を与える操縦やブレーキなどの決定を行う前に、複数の

車両センサーのデータを交えて(Fusion)処理を実施します。

5

Page6

記録パス ブレーキシステム

アクセラレー

ションシステム ステアリングシステム

中央処理装置

画像処理システム

カメラ� カメラ� カメラ� カメラN

図1: 車載ビジョンシステムアーキテクチャ

車載アプリケーションでは、ケーブル配線の最小化は、質量とコス を莫大な設計費用を掛けても達成させるか、どちらかを選択する

トが大幅に増加するため非常に重要です。 広帯域の出力信号、 ことになります。 これは、MIPI D-PHY が同じ入出力セル内で低

制御チャネル、そして電源等が複数必要となる車載カメラ。 更に スイング高速差動信号とシングルエンド低速制御信号をサポート

複数の車載カメラを搭載する計画がある場合、配線数の増大を招 する必要があり、デバイス搭載が困難であることに起因します。

き困難が増す結果となります。 そのため、メーカーはMIPI CSI-2

標準のカメラ及びセンサーを使用します。 このアプローチによ また、センサーから情報を抽出および処理する機能にはかなりの

り、高解像度、高フレームレートのカメラに必要な高データレート 処理能力が必要であり、且つ車両は適時に決定を下せるような設

を維持しながら、ケーブル配線をドラスティックに削減できます。 計が必要です。 その画像処理システムは低レイテンシで高性能・

例えば、ONsemi社は各カメラに1本の同軸ケーブルで接続が可 高精度な推論処理を実現する必要があります。 このため、多くの

能なギガビットマルチメディアシリアルリンク(GMSL)技術のドラ 場合、これらの要件を満たすために専用の高性能プロセッサまた

イバーとレシーバーを利用して電源、制御、およびビデオ信号をシ は ASIC が必要になります。 画像処理パイプラインの途中に外

ンプルにします。 これらのドライバーとレシーバーICを利用する 部DDRを配置して中間処理データを格納するようなアーキテクチ

場合、GMSL伝送はMIPI信号をベースに変換され入出力されるた ャは、共有システムリソースであるDDR の性質とそのアクセス時

め、複数で広範囲をカバーする車載カメラやその処理システムと 間により処理レイテンシ増大とアクションの遅れを発生させます。

の間のインターフェイスを容易にします。

通常の設計では画像処理アルゴリズムはプロセッサの上のソフト

これら機能の活用により、複数のカメラ制御とインターフェイスと ウェアフレームワークに実装します。 OpenCVは、開発時間を最

共に、GMSLリンクを制御できることが必要になります。 もちろ 小限に抑え付加価値のあるアクティビティに集中するために、画

ん、システムは、CAN、CAN-FD、車載イーサネット、FlexRay 等の標 像処理アプリケーションで一般的に使用されるフレームワークの

準的な車載インターフェイスを使用して、ダウンストリーム車両制 1つです。 OpenCVは、迅速かつ簡単に導入できるC、C++、および

御システムと通信は必須となります。 Pythonの画像処理機能を提供します。 開発者は、このアプロー

チにより、付加価値のあるアクティビティと専門的なアルゴリズム

複数の高速 MIPI インターフェイスと接続しつつ、必要なダウンスト に集中できるため、開発プロセスの時間を短縮できます。

リーム通信インターフェイスが必要とされる場合、それを実現する

ための新規設計をとるか、既存デバイスに合わせた設計をとるか、

というトレードオフに直面します。 結果として、パフォーマンスを

妥協し既製のソリューションに合わせるか、独自にカスタムソリュ

ーションを開発して必要なインターフェイスとパフォーマンス仕様

6

Page7

課題への対応

インターフェイス、パフォーマンス、レイテンシ、および決定性の課題は、ザイリンクスのオ xfOpenCVライブラリ

ートモーティブ向けXA Zynq UltraScale+ MPSoCなどのヘテロジニアス・システムオンチ

ップを使用して対処が可能です。 これらのデバイスは、さまざまな処理システムと複数 ザイリンクスは、OpenCV などのフレーム

拠点間インターフェイス接続機能に連結されたプログラマブルロジック、そして機械学習 ワークで作成された高レベルのアルゴリ

推論などの機能を高速化するための専用リソースを提供します。 ズムモデルを利用できるように、xfOpenCV ライブラリを提供しています。xfOpenCVラ

開発者は、このプロセッシングシステム(PS)とプログラマブル

イブラリには、ザイリンクスの統合ソフトウ

ェア開発ツールVitisの高位合成を使用し

ロジック(PL)間の適切な処理分割を行う事で、CORTEX-A53や てプログラマブルロジックに合成できる、

CORTEX-A72等の高性能プロセッサで高レベルのアルゴリズムを

一般的に使用されるOpenCV関数がいく

つか含まれています。これにより、OpenCV

実行しながら、プログラマブルロジックを使って複雑な画像処理を を使用した高レベルのモデリングが可能

パイプライン処理することが可能となります。 になり、ハードウェア記述言語を書き込むことなく、同じ機能をプログラマブルロジ

ックパイプライン内にすばやく簡単に実装

プログラマブルロジックI/Oの柔軟性により、ザイリンクスの Zynq UltraScale+の高性能 できます。

I/O Bankデバイスは、MIPI D-PHYを直接サポートできます。 つまり、外部PHYが不要に

なり、オンボード領域を節約し、複数のMIPIインターフェイスを使用した場合に、よりコン

パクトなソリューションを提供できます。プログラマブルロジックで使用可能な多数のI/O

ピンにより、大量のMIPIインターフェイスを実装できるため、従来のCPUおよびGPUソリュ

ーションによる制約から設計者は解放されます。

プログラマブルロジック(PL)デザイン内では、MIPI-CSI2 IPコアを使用してMIPI ビデオ ス

トリームをデコードできます。MIPI-CSI2 IPブロックの出力はAXIストリームとしてビデオ

形式となり、プログラマブルロジック(PL)内では標準ストリーミングインターフェイスを使

用することで、ザイリンクスのIP ライブラリ若しくは3rd party IP ブロック、または カスタ

ムアルゴリズムが必要な場合は高位合成を活用することによって、画像処理パイプライン

を簡単に構築できます。 これにより、プログラマブルロジック内にお客様が求める真の

画像処理パイプラインを作り上げることが出来ます。 これにより、レイテンシや、処理性

能が大幅に向上します。

画像処理またはダウンストリーム処理にH .264/H .265エンコーデ

ィングまたはデコーディングが必要な場合、XA Zynq UltraScale

+ MPSoCのEV製品は、ストリームのバッファリング用に、関連する

UltraRAMとともに組み込みビデオコーデックユニットを提供します。

自律自動車機能の多くは、画像処理アルゴリズムパイプラインで検出されたオブジェク

トを識別および分類できるシステムインテリジェンスを必要とします。 ザイリンクスの

デバイスの場合、Vitis AIはCaffeやTensorFlowなどの一般的に使用されるML / AIフレ

ームワークの高速化を可能にします。また、Vitis AIは、深層学習処理ユニットにアプリケ

ーションを展開するためのModel Zoo、AIコンパイラ、オプティマイザ、クウォンタイザ(

量子化器)、およびプロファイラを提供します。

7

Page8

画像処理パイプライン、機械学習、および上位レベルのアルゴリズ れており、ロックステップで動作するデュアルARM Cortex-R5プロ

ムから抽出された情報は、サポートされている規格を選び(たと セッサが含まれています。必要に応じて、RPUは、ビジョン処理シス

えば、プログラミングシステム(PS)またはプログラマブルロジック テム内で直接機能安全を考慮した処理を実装することが可能で

(PL)で利用可能な車載イーサネット、CANまたはCAN FDを介して す。典型的な例には、カメラと通信リンクのステータスの監視など

設置されたセントラルECUと通信を行う事ができます。 があります。アプリケーションプロセッサ(A53)とリアルタイムプロ

セッサ(R5) 間の通信をサポートするためにOpenAMPフレームワ

ビジョンアプリケーションのプロトタイピングとテストに、高性能テ ークを使用して、マルチプロセッサ環境での通信を管理できます。

ストまたはディスプレイインターフェイスが必要となります その

場合はプロセッシングシステム(PS)またはプログラマブルロジック プロセッシングシステム(PS)に搭載されているSATAおよびPCIeイ

(PL)で利用可能な次の高速インターフェイスを使用して簡単に実 ンターフェイスは、システムの監視、ロギング、およびメンテナンス

現できます。 に必要な場合に、システム情報やビデオフレームまで記録する機

能を提供します。

DISPLAYPORTインターフェイスは、プログラマブ

ルロジック(PL)からのライブビデオ、またはプログ

ラミングシステム(PS)からの処理済みフレームの

まとめ

両方を出力するのに使用できます。その他、GIGE

ビジョンシステムは、自律車両の発展に重要な役割を果たしてい

ます しかし、搭載カメラ数の増大により、いくつかの課題解消

VISION、10 GIG ETHERNETおよびPCIEなどを が求められます。複数の高帯域インターフェイス、低レイテンシ処

介したビデオ出力実装も可能です。 理、高速画像処理・判断等です。設計者は、XA Zynq UltraScale+

MPSoCなどのヘテロジニアスSoCを使用して、デバイスの機能だ

安全性は自律車両運行の最重要課題です、特に車載ビジョンは最 けでなく、本デバイスをサポートするエコシステムの活用から、自

重要に位置付けられる機能です XA Zynq UltraScale + MPSoC 動車ビジョンアプリケーションに必要なインターフェイス、低レイテ

ではデバイス内のPlatform management unit(PMU)を利用し、 ンシ、高精度・高速な判断、および安全性を備えたソリューション

デバイスの内部電源電圧とダイ温度を監視することが出来ます。 の開発を実現できます。

また、Common Cause Failureに対処するため、プロセッシングシ

ステム(PS)とプログラマブルロジック(PL)間を電気的に分離する

ことで、プロセッシングシステム(PS)とプログラマブルロジック(PL)

を互いに独立させてパフォーマンスとステータスを監視する設計

が可能です。

また、プロセッシングシステム(PS)内に位置するリアルタイム処理

ユニット(RPU)は、ISO 26262アプリケーションを考慮して設計さ

8

Page9

ADAS用レーダー

はじめに レーダーシステムは、無線周

レーダーは、自律運転の鍵となる技術です。LiDARやビジョンシステムとは異なり、レー 波数信号を生成、送信、受信、

ダーは霧や大雨など、あらゆる照明や気象条件において機能を発揮します。vしかし、 および処理する能力を必要と

高い SAE 自律レベルを実現するに必要な精度を実現するために4 次元レーダーが良

く利用されます。 4 次元レーダーは方位角、標高、傾斜範囲だけでなく、ドップラー周 します

波数に関する情報も提供します。 このドップラー周波数を活用することでターゲットの

速度を検出することができます。

4Dレーダーは、(100度の)広い視野、細かい(1度)空間分解能、および長距離(300m程

度)測定機能を持つシステムを提供します。これにより、SAE レベル2および3で自律運

用が可能になり、交通渋滞アシスト、高速道路の運転、セルフパーキングなどの機能が

実現されます。

アーキテクチャの機能と考慮事項

レーダーシステムには、無線周波数信号を生成、送信、受信、処理する機能が必要で

す。従来は、信号生成および処理のために、RFフロントエンドと共にベースバンドデジ

タルプロセッシングを使用して、ベースバンドからのアップおよびダウンコンバージョン

を行う必要がありました。信号は、アナログ-デジタル変換器(ADC)およびデジタル-ア

ナログ変換器(DAC)を使用して、アナログ領域からデジタル変換されます。デジタルベ

ースバンド信号処理には、レーダーチャープ生成と結果の後処理が含まれます。

ただし、4Dレーダーでは、ビームをスイープ全体にステアリングす

るために、モノパルスのビーム形成アプローチがよく使用されま

す。 其々のスイープでは、定義された期間をカバーするフレーム

内で複数のチャープが連続して送られます。

9

Page10

周波数 振幅

f0

時間

アップチャープ

時間

図 1: チャープ信号

ベースバンド処理は、2 次元FFTを使用して受信したチャープを処理できます。 チャープ応答の最初の FFT は、距離情報を提供します。

通常、この FFT は、2つのうち大きい方(たとえば 4096 ポイント)になります。 最初の FFT の結果には、2番目のFFTが適用され、フレ

ーム全体にわたって見渡され、相対速度が提供されます。 この2番目のFFTは最初のFFTより小さく、通常は1024ポイント未満です。

方位角と標高は、モノパルス受信機によって提供される合計チャネルと差分チャネルから決定できます。

ベースバンド処理では、チャープ生成や 2D FFT の他に、デシメーションや補間、一定の誤警報率(CFAR)の適用などのアルゴリズム、お

よび車両内のダウンストリームモジュールの処理や通信を行い、識別されたターゲットに安全に対処できるようにする必要があります。

車両が走行環境で安全に動作するためには、レーダーからの情報が必要です。 したがって、ベースバ

ンド処理内で実装されるアルゴリズムは、低レイテンシ応答を提供できる必要があります。

レーダーシステムのビジュアルプロットは、プロトタイピングと評価の一部として、または車両のインフォテインメントシステムの一部とし

て、生成する必要がある場合もあります。 このプロットには、検出されたターゲットの位置、速度、およびトラックが表示されます。

電子レベルでは、ベースバンド処理は高速ADCおよびDACデバイスとのインターフェイスが可能でなければなりません。 これにより、高

速ルーティングのシグナルインテグリティや、低ノイズアナログおよびRFセクションからのデジタル信号のセグメント化など、回路基板の

設計にリスクが伴います。 これらはすべて、システム全体のタイトなサイズ、重量、電力、およびコスト(SWaP-C)目標内で達成する必要

があります。

これらのパフォーマンスとSWaP-C要件に対処することは困難であり、ソリューションアーキテクチャ全体のトレードオフにつながる可能

性があります。

課題への対応

ザイリンクスのZynq UltraScale+ RFSoC*は、設計者がパフォーマンスとSWaP-Cの両方の課題に対処するのに役立ちます。 RFSoCデ

バイス・ファミリには、高性能クアッドコアARM Cortex-A53 64ビットプロセッサを備えた処理システムだけでなく、アップおよびダウンコ

ンバータ、複雑なミキサ処理、補間処理、デシメータなどの必要機能ブロックと、ギガサンプル/秒のADCおよびDACを備えたプログラマ

ブルロジック(PL)が含まれます。 これにより、RFフロントエンドとのインターフェイスの複雑さが大幅に緩和されるだけでなく、要求され

る実装領域も全体的に縮小できます。

このようなシステムによって、処理システム内の アプリケーション処理ユニット(APU)は、CAN や車載イーサネットなどの標準インターフ

ェイスを使用して、ダウンストリーム車両システムとの高レベルのアプリケーションおよび通信フレームワークを実装できます。APU内で

実行されるアプリケーションは、組み込みLinuxオペレーティングシステムとザイリンクスのPetaLinuxビルドフローを使用できます。 ま

たは、RTEMS や QNX などの適切なスタックを使用して他のオペレーティング システムを展開することもできます。

*Zynq UltraScale+ RFSoCデバイスは、ザイリンクスのオートモーティブグレードのポートフォリオに含まれていません。 10

Page11

DDRメモリ

PS ‒ プロット計算 読み込み

システム制御および通信 アプリケーション

映像出力端子

書き出し

RF端子(入力) ADCインターフェース RF処理パイプライン DMA RFデータ

RF端子(出力) DACインターフェース RF波形生成

チャープ DAC IF 波形生成

PS

RFサンプル ADC IF ストレージ DDR

DMA

FFT

FFT

HDMI/DVI出力 AXIS Parallel用 VDMA

SDIO

SDカード

VTC

図 2 & 3: RFSoCでパフォーマンスとSWaP-Cの両方の課題に対処する方法のブロック図

11

Page12

レーダーシステムのリアルタイム制御を提供するために、処理システム内のリアルタイム

処理ユニット(RPU)を使用できます。このRPUは、ISO 26262認証を取得するために必要 プログラマブルロジック

な安全上重要な機能を実装するために設計されており、ロックステップデュアルコアARM デバイスのプログラマブルロジックエレメ

Cortex-R5プロセッサを搭載しています。RPU内のこれらのプロセッサを使用して、システ ントは、チャープ生成と、2D-FFT、CFAR、位

ムモニターおよびプラットフォームマネジメントユニット(PMU)と連携して、単一点障害お 置抽出などの結果として生じる信号処理

よび潜在的な障害を監視する機能安全を実現で可能です。 パイプラインの実装を可能にします。プロ

グラマブルロジックは、アルゴリズムの並

低レイテンシソリューションをサポートしているのは、プログラマブルロジック内の再構成 列実装を可能にし、そのような実装は低レ

可能なロジックブロックだけでなく、専用のDSPエレメントや、分散RAM、ブロックRAMや イテンシの応答と高い精度を実現します。

UltraRAM等の多様なストレージ機能です。

RFSoCファミリのデバイスは、プログラマブルロジック領域内に3,145〜4,272個の分散

配置された専用の48ビットDSPエレメントを用意しています。これらのDSPエレメント

は、FFT、シストリックおよびマルチレートFIRフィルター、CICフィルター、および実数と複

素数の乗算器と累算器の実装をサポートできるように設計されています。48ビットの解像

度が必要ない場合、設計者は単一命令複数データ(SIMD)演算モードを利用して、デュア

ル24ビット演算またはクワッド12ビット演算を実行するように設定可能です。

小型なローカル・ストレージを持つことで、より高性能

なシステムを実現可能していますプログラマブルロジ

ック内のブロックRAMおよびUltraRAMは、小型ローカ

ル・ストレージとしての利用に最適です。

ブロックRAMは、アルゴリズム段階の間にデータを格納する小さなバッファ、メモリ、およ

びFIFOに適していますが、UltraRAMは、大量のデータを格納する必要がある場合に外部

メモリの代替として利用できるように設計されています。 UltraRAMブロックは、36Kb

のブロックRAMとよりも大きく、4K x 72bitブロックでTotal 288Kbの容量を持ちます。

アーキテクチャ上、UltraRAMブロックはカスケードすることが出来、ADCからキャプチャ

したデータを格納したり、DACで出力したりするために使用される大規模内部メモリを

要因に設計できます。 RFSoCファミリの UltraRAM の総容量はデバイスにより最小13 .5

Mbから最大22 .5 Mbまで幅があります。

RFSOCの主なエレメントは、ADCおよびDACコンバータであり、ギ

ガサンリング(GSPS)を実現可能です。

RFSoCはデバイスの世代に応じて、このサンプルレートが向上します。 第1世代デバイス

の2 GSPS ADCから第3世代のデバイスの5 GSPS ADCまで進化し、4つのナイキストゾー

ンすべてでの動作を可能にするRF入力帯域幅をサポートします。 また、DACのサンプリ

ングレートも、第1世代は6 .5 GSPS、第2世代は10 GSPSと向上します。 このサンプリン

グレートと広いRF入力帯域幅の組み合わせにより、RF TxおよびRxパスの複度が大幅に

軽減されます。

プログラマブルロジック内のベースバンド処理を容易にするために、各ADCまたはDAC

は、デジタルアップおよびダウンコンバータ、デシメータおよび補間処理、複雑なミキサ、

数値制御のオシレータが容易されています。 これにより、RFフロントエンド設計は、低レ

ベルのハードウェア記述言語(HDL)ではなく、高レベルのシステム設計アプローチに従

い構成することができます。

12

Page13

システム起動時、ADC、DACそしてアップ/ダウンコンバータ、ミキサ、およびNCOは、プロ

セッシングシステム(PS)上で実行されるソフトウェアを介して各種設定や最適化が行わ VITIS

れます。 Vitisは、アプリケーションプロセッサユニッ

ト(APU)とリアルタイムプロセッサユニット

プログラマブル・ロジック・コンテンツの開発においては、Vivado Design Suiteが提供す (RPU)の両方で処理されるシステムアプリ

る広範なIPカタログを活用できます。あるいは、特殊なアルゴリズムが必要な場合は、C ケーションの作成を可能にする統合ソフト

やC++、またはMATLABのような高水準言語を使用して実装することもできます。これら ウェア開発環境です。また、VitisはOpenCL

のツールは、Vitis統合ソフトウェア・プラットフォームといった、高位合成ツールの機能を をサポートし、プログラマブルロジックに高

利用しています。 位合成を使用したアクセラレーションカー

ネル搭載を可能とします。

システムで視覚的なレーダープロットが必要な場合、プロセッシングシステム(PS)内の

DisplayPortインターフェイスを使用して、この出力を表示できます。DisplayPort 出力で

は、プロセッサシステムとプログラマブルロジックの両方からビデオフレームを出力でき

ます。または、柔軟なプログラマブルロジックI/Oを利用して、HDMI / DVIまたはその他の

カスタム・ビデオ出力規格を実装することもできます。

まとめ

プロセッサ、プログラマブルロジック、RFデータコンバータの緊密な統合により、自動車用

4Dレーダーに必要な高性能と低レイテンシを備えるシステムを構築できます。設計ツー

ルをサポートするエコシステムにより、プロセッサ、プログラマブルロジック、およびシステ

ムアプリケーションを簡単に作成できます。

13

Page14

自動車アプリケーションの集約、融合、アクセラレーション

はじめに

自律機能は、自動車開発で最もホットなトピックの1つであり、既存および新規の自動車メーカーが自律走行車の開発でしのぎを削って

います。 これらの開発者はムーアの法則の恩恵を受けており、これにより処理能力とセンサーテクノロジーが大幅に向上すると同時

に、コストを削減することができます。

GPS, レーダー, LiDAR, ビジョンシステムなどのさまざまなセンサーを使用して、車両がリアルタイムで環境を理解し、安全にやり取りで

きるようになるため、この処理能力とセンシング能力の向上は非常に重要です。 センサー、アルゴリズム処理能力を変えることで、様々

なレベルの自律機能を実現することが可能となります。

自律機能は、完全な自律運転からドライバーとの共有制御まで、複雑で広範囲にわたる技術領域です。 米国自動車技術者協会(SAE)

は、次のいくつかのレベルの自律機能を定義しています。

SAE

自動

運転

レベ フォールバック(

ル 名称 例 車両の制御 モニタリング 縮退運転) 車両の機能

0 自動化なし 該当なし 運転者(人) 運転者(人) 運転者(人) 該当なし

アダプティブクルー

1 運転者支援

ズコントロール/レ 運転者(人)と

ーンキープ & パーキ 車両

運転者(人) 運転者(人) 一部の走行モード

ングアシスト

2 部分自動運転 交通渋滞アシスト 車両 運転者(人) 運転者(人) 一部の走行モード

完全停止と発進 高

3 条件付き自動運転 速道路走行 セルフ 車両 車両 運転者(人) 一部の走行モード

パーキング

4 高度自動運転 自動運転 車両 車両 車両 一部の走行モード

5 完全自動運転 無人運転 車両 車両 車両 すべての走行モード

図1 . SAE自律機能のレベル

14

Page15

自律運転に採用されるモダリティ(各種センサー)は、車両の全体的な挙動・周囲に関する

データを提供します。 走行環境の全体像を形成するには、多様な要素を融合する必要 課題

があります。さまざまなセンサーの配置とモダリティは、実装される自律性のレベルによっ 自律システムは大量生産されるため、メー

て異なります。ただし、カメラは車線逸脱警告、死角検出、交通標識認識などのアプリケ カーが定義したサイズ、重量、電力、および

ーションに使用され、4Dレーダーは追跡対象の距離、速度、方向を特定できます。 コスト(SWaP-C)の仕様に準拠する必要が

あります。自律機能の開発者が直面するこ

部分的な自動化(レベル2)以上の場合、車両がその位置と周囲の障害物を完璧に識別 れらの課題は、次のように要約できます:

することが、安全なナビゲーション実現に不可欠となります。 システムは、GPSデータと

ともにカメラ、レーダー、およびLiDARを使用して走行環境を理解します。 また、GPSデ - 複数の高帯域幅センサーモダリティとの

ータそれ自体は建物やインフラに遮られることで容易に精度が低下します。 インターフェイス性能

使用されるさまざまなセンサーのモダリティは、自律機能の開発者に大きな課題をもた - 高帯域幅センサーデータに複雑な後

らします。各センサーのモダリティは、異なる形式でデータを提示し、異なるインターフェ 処理アルゴリズム(画像処理パイプライン、4Dレーダー、etcなど)を 実行可能な

イス(MIPI, LVDS, SPI, I2C等)を使用します。 処理能力

レーダー/ LiDARやビジョンシステムなどの高帯域幅インターフェイスでは、ターゲットを - 複雑な後処理および高度な意思決定を

識別しオブジェクトを分類および検出するためにかなりの前処理が必要です。 同時に、 リアルタイムで実装できる処理能力

これらの高帯域幅インターフェイスには、システム全体の応答性と決定性に影響を与え

る可能性のある複雑なチェーンの専用処理が必要です。 - ISO 26262などの規格への準拠

異なるセンサーモダリティからの情報は前処理、照合・相互(冗長)確認を施した後に、高 - 要求の厳しいSWaP-C目標の達成

位の意思決定アルゴリズムにより処理され、車両の周囲環境に合わせた安全運行に利

用されます。

自律システムに機能的な障害が発生すると、死亡または負傷事故に至る重大な被害に

至る可能性があります。 このような障害のリスクを最小限に抑えるために、システムの

開発はISO 26262などの規制基準に準拠する必要があります。

アーキテクチャの機能および考慮事項

自律機能を実装する中心には、中央処理システムがあります。 自律機能を正常に実装

するには、中央処理システムが次の機能を実行する必要があります。

- センサーとのインタフェースとその処理 — プロセッシングシステム(PS)とプログラマグ

ルロジック(PL)を使ったアクセラレーション処理を含めた信号処理やそのデータのルー

ティング・スイッチングが課題となります。例えば:画像処理の前処理パイプライン、物体

検知や4D RADARの2次元FFT, CFARやトラッキング処理などの後段処理等。

- 高性能シリアル処理 — データの抽出、センサーフュージョン、高レベルの意思決定。一

部のアプリケーションでは、ニューラルネットワークが高性能シリアル処理内に実装され

ます。

- 安全処理機能 — DAPD(Distributed and parallel database)の前処理結果ベースとした

周囲検知のリアルタイム処理と後段の高性能なシリアル処理で提供されるニューラルネ

ットワークアクセラレーションにより高速処理による高速処理が必要となります。DAPD

とさまざまなセンサー・検知機器とのインタフェースもプロセッシングシステム(PS)とプ

ログラマグルロジック(PL)を使ったアクセラレーション処理で信号処理やそのデータのル

ーティング・スイッチングが課題が課題となります。

- ニューラルネットワークアクセラレーション — 物体の検出と分類(歩行者, 車等の検出、

道路標識の分類等)のためにニューラルネットワークをアクセラレーション処理します。

アプリケーションの要求により、これらの機能は、車載イーサネットなどの自動車通信規

格を使用して接続された複数のデバイスに実装されます。

15

Page16

カメラ 車両制御

レーダー

ブレーキ超音波 PHY センシング・インターフェースおよび処理 安全処理 PHY ステアリング

LIDAR 加速

GPS

ニューラル・ネットワーク・アクセラレーション 高性能処理 PHY ヒューマン・マシン・インターフェース

図2 . 車載イーサネット接続を使用して接続されたデバイス

課題への対応

XA Zynq UltraScale+ MPSoCsは、センサーインターフェイスと処理だけでなく、同じシリコン内で高性能、安全処理、ニューラルネットワ

ークアクセラレーションも実現を可能としました。 また、SAEレベルの増加に応じたデバイスを選ぶ事で複数の機能をシングルデバイ

スに実装可能とします。 この高度に統合されたスケーラブルなソリューションは、SWaP-Cを大幅に改善します。

Zynq UltraScale+ MPSoCは、リアルタイム制御のために、以下の機能を提供します。

1 . ASIL Cまでの安全機能を実装できるロックステップデュアルARM Cortex-R5プロセッサを内蔵、セーフティクリティカルなアプリケーショ

ン向けのリアルタイム処理ユニット(RPU)。 RPUは、必要な機能安全を提供するために、ハードウェアや単一イベントなどによって引き

起こされる、単一のランダムな障害を削減、検出、および軽減する機能を備えるように設計されています。これらのデバイスは、プロセッ

サシステム(PS)リソースおよび/またはプログラマブルロジック(PL)間の機能の効率的なセグメンテーションを可能にします。

センサーインターフェイスと処理によって提示される重要な課題の 1 つは、高帯域幅センサーのモダリティとのインターフェイス実現性

です。これらセンサーは其々、異なるインターフェイス標準となっていることが課題となります。

一般的なソリューションは、カメラ、レーダー、LiDAR などの高帯域幅インターフェイスに対して、MIPI、JESD204B、LVDS、GigE などの高

速インターフェイスを使用するさまざまなセンサー方式と接続します。 センサーインターフェイスは、CAN, SPI, I2C, UARTなどの低速イ

ンターフェイスとインターフェイスする必要もあります。

2 . 機能安全プロセッサの実現は、さらなる課題を提示します。 機能安全プロセッサは、分散および並列データベース(DAPD)から受信し

たコマンドと、車両の安全な制御を可能にする高性能シリアル処理に対応する必要があります。 機能安全プロセッサは、自動運転の重

要な側面であるステアリング、アクセラレーション、ブレーキなどの車両制御と直接相互作用します。ここでのエラーは、生命の喪失また

は環境への損傷をもたらす可能性があるためです。 ザイリンクスのオートモーティブグレードのZynq UltraScale+ MPSoCには、RPU内

にデュアルロックステップARM Cortex-R5コアが含まれており、機能安全処理の実装に利用できます。

RPUコアのロックステップ機能に加えて、ザイリンクスのZynq UltraScale+ MPSoCの追加の損害軽減措置には、RPUのエラー修正コー

ドの導入、密接に結合されたメモリとキャッシュが含まれており、DDRメモリは二重エラー検出と単一エラー修正コードで保護されてい

ます。

3 . CAN, SPI, I2C, UART, GigEなどのさまざまな業界標準インターフェイスをサポートし、PL I/Oの柔軟性によりMIPI, LVDS, ギガビットシリ

アルリンクとの直接インターフェイスが可能になります。 多くの場合IPコアを使用して、より高いレベルのプロトコルを含めてプログラ

マブルロジック(PL)内に実装可能です。 プログラマブルロジック(PL)内にプロトコルを実装すると、標準リビジョンを簡単に組み込むこ

とができ、ソリューション内でサポートされる特定のセンサーインターフェイスの数に対する柔軟性も向上します。 プログラマブルロジ

ック(PL)はまた、ハードウェアデザインに適切なPHY設定を行うことで、任意のインターフェイス実装も実現可能で、真のAny to Any( 複

数拠点間)インターフェイス接続機能を提供します。

4 . ザイリンクスのDNNDKおよびVitis AIを使用してニューラルネットワークの高速化が可能です。 また、Vitisを使用して画僧処理アルゴリ

ズムを高速化することもできます。 Vitisを使用すると、OpenCLカーネルをプログラマブルロジックにオフロード実装できます。

16

Page17

GIC

CPU�に関連するTCM CPU�に関連するTCM CPU�に関連するキャッシュ

D-キャッシュ

比較および同期ロジック I-キャッシュ

図3 .リアルタイム処理ユニットのアーキテクチャ

5 . 電源投入時の組み込み自己テスト(BIST)により、ベースとなるハードウェアに事前障害がないことを確認します。追加のBISTは、操作中

にユーザの要請によって実行することも可能です。また、Zynq UltraScale+ MPSoCのアーキテクチャは、デバイス内部のメモリと周辺の

機能分離を行う機能も提供します。

6 . 重要なセキュリティ機能には、以下が含まれます:

- 改竄・情報漏洩防止(プライバシー保護)のための安全な構成(AES暗号化)

- Differential power analysis(電力差分解析)を防ぐためのキーローリング

- デバイスのセキュリティ状態を管理するセキュリティユニットの設定

17

シム シム

Page18

これらの対策をザイリンクスのオートモーティブグレードのZynq UltraScale+ MPSoCに

実装することで、センサーインターフェイスおよび補正処理、高性能信号処理、ニューラル

ネットワークアクセラレーションと同様にシリコン内にセキュリティ機能を持たせることが

可能です。また、機能安全実現のため、通常では複数デバイスが必要になる場合にも、機

能分離(セグメンテーション)を行うことで、一つのシリコンに統合化することも検討可能

です。

もちろん、その統合化により必要となるPCB面積と

相互接続の複雑さも軽減され、同時に電力消費量

が削減されます。

まとめ

自律運転機能の実現には、集中処理モジュールの設計が必要となります。 これにはさ

まざまなセンサーモダリティとのンターフェイスや従来のSWaP-C問題を含む、いくつかの

課題がつきものです。 センサーインターフェイス、ニューラルネットワークアクセラレー

ター、および機能安全プロセッサのその全てをザイリンクスのオートモーティブグレード

Zynq UltraScale+ MPSoCに機能統合して集約することで、より小型且つ軽量で電力効率

の高いソリューションの設計が可能となります。

18

Page19

自律運転車の機能安全

はじめに

自動車システムメーカーが直面する重要な課題の1つは、関連する安全および品質基準に準拠するシステムを設計することです。

自動車業界での機能安全の場合、これはISO 26262車載のコンポーネントに関する機能安全規格(ASIL)の1つに準拠することを意味し

ますISO 26262 は、リスクベースの安全基準として、生産車両の電気システムおよび/または電子システムに適用され、運転者支援、推

進、および車両力学制御システムを網羅します。4つのASILは、システムの危険性のレベルを示します。

自動車

安全水準 重要度 FIT メトリック 結果

(ASIL)

単一障害点

ASIL-D 最重要 < 10 FIT メトリック> 99% Possible Fatalities in 潜在的障害メトリック> Community

90%

単一障害点

ASIL-C < 100 FIT メトリック> 97% 潜在的障害メトリック> Possible Fatalities

80%

単一障害点

ASIL-B < 100 FIT メトリック> 90% Possible Major Injuries 潜在的障害メトリック> or a Fatality

60%

単一障害点

ASIL-A 最も低い重要度 < 1000 FIT メトリック> 90% 潜在的障害メトリック> Potential for Minor Injuries

60%

QM 品質管理 該当せず 安全性に関連しない

図1 . 自動車安全水準

19

Page20

単一障害点メトリックは、単一障害点に

よるリスクを防止する安全設計の機能で

すが、潜在的障害メトリックは、安全設

計によって検出されない複数点障害です。

システムの ASIL レベルは、危険分析を実行して決定され、次の点に対応します。

- 重症度 — 搭乗者に起こりうる負傷の度合いの程度?

- 曝露 — システム/車両が危険にさらされる暴露率?

- 制御性 — 負傷を防ぐためにドライバー/車両はどんなアクションを取るべきか?

車両内の各システムのASILレーティングは異なります。 例えば、ブレーキ、ステアリング、エアバッグなどの重要なシステムは通常ASIL-D

ですが、ヘッドライトとADASシステムは通常ASIL-Bです。

必要なASILを実現する設計を実践するには、単一点・デュアルポイント故障を検出・軽減できるよう、大規模な設計分析と障害モードの

熟考が必要です。

アプローチと課題

目的のASILを実現するには、設計当初から障害軽減と障害検知方法を踏まえた、アーキテクチャ設計レベルでの検討が必要となりま

す。 開発サイクルの後半にこのような障害軽減と保護機能を追加すると、プロジェクトのスケジュールとシステムコストに大きな影響

を及ぼす恐れがあります。

設計の主要な要素の1つは、設計初期から可能な限り多くの単一点障害を取り除くこととなります。 アーキテクチャレベルとしては、ハ

ードウェアフォールトトレランスまたは冗長化回路の実装を意味する場合があります。

電子システム内の一般的な単一点障害には、入力と出力、クロック、電源、リセットと電源シーケンス、および構成メモリがあります。 こ

れらの領域での障害は、ハードウェアのフォールトトレランスまたはさまざまなパスに伝播し、影響を与えた場合、システム全体に障害を

もたらす可能性があります。

単一障害点 軽減

入力 / 出力 重複

クロック 多重クロック

電源供給装置 独立サプライ

個別のリセットおよびシーケンス リセットおよびシーケンスシステム

構成メモリ エラー検出と修正

プロセッサ ロックステップ操作

ロジック設計 三重モジュール式冗長

図2 . 単一点障害と損害軽減

設計者はまた、設計回路内の障害伝播の影響を考慮する必要があります。 物理的な(Isolation)分離などの技術は、1 つの障害が軽減

回路要素に影響を与えるのを防ぐために使用されます。

必要なASILを実現するには、必要な回路の設計作業以上に分析および検証作業が必要となります。 また、プロセッサ、FPGA、およびそ

の他のプログラマブルデバイス向けのソリューションを作成するための設計ツールも重要です。 これらのツールは、必要に応じて機能

安全認定済の物を選択します。 そのツール自身の問題により、設計上のエラーが生じたり、検出できなかったりする可能性があること

を考慮すると、この選定は重要になります。

20