1/2ページ

ダウンロード(888.8Kb)

プロトタイピング環境の開発の効率向上と迅速な起動

HES Proto AXI とアルデックの HES プロトタイピングボードと組み合わせてご使用いただくと、アルゴリズムアクセラレーションやハイパフォーマンスコンピューティングなどのアプリケーションの迅速なテストとFPGA ベースのプロトタイピング の構築が容易になり、検証効率の向上を行うことが可能になります。

このカタログについて

| ドキュメント名 | HES Proto-AXI |

|---|---|

| ドキュメント種別 | 製品カタログ |

| ファイルサイズ | 888.8Kb |

| 登録カテゴリ | |

| 取り扱い企業 | アルデック・ジャパン株式会社 (この企業の取り扱いカタログ一覧) |

この企業の関連カタログ

このカタログの内容

Page1

スライド 1

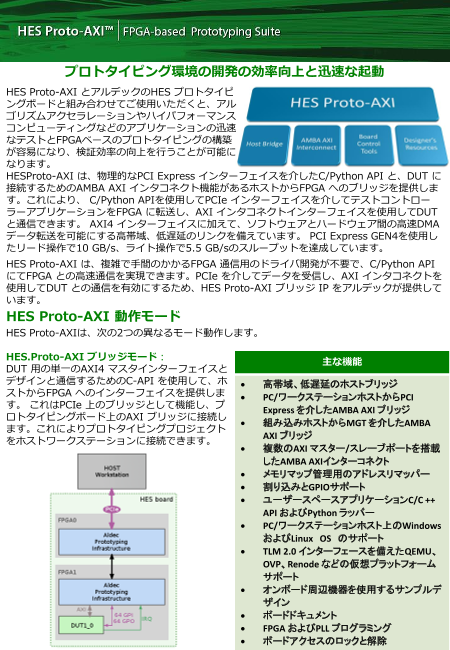

プロトタイピング環境の開発の効率向上と迅速な起動

HES Proto-AXI とアルデックのHES プロトタイピ

ングボードと組み合わせてご使用いただくと、アル

ゴリズムアクセラレーションやハイパフォーマンス

コンピューティングなどのアプリケーションの迅速

なテストとFPGAベースのプロトタイピングの構築

が容易になり、検証効率の向上を行うことが可能に

なります。

HESProto-AXI は、物理的なPCI Express インターフェイスを介したC/Python API と、DUT に

接続するためのAMBA AXI インタコネクト機能があるホストからFPGA へのブリッジを提供しま

す。これにより、 C/Python APIを使用してPCIe インターフェイスを介してテストコントロー

ラーアプリケーションをFPGA に転送し、AXI インタコネクトインターフェイスを使用してDUT

と通信できます。 AXI4 インターフェイスに加えて、ソフトウェアとハードウェア間の高速DMA

データ転送を可能にする高帯域、低遅延のリンクを備えています。 PCI Express GEN4を使用し

たリード操作で10 GB/s、ライト操作で5.5 GB/sのスループットを達成しています。

HES Proto-AXI は、複雑で手間のかかるFPGA 通信用のドライバ開発が不要で、C/Python API

にてFPGA との高速通信を実現できます。PCIe を介してデータを受信し、AXI インタコネクトを

使用してDUT との通信を有効にするため、HES Proto-AXI ブリッジ IP をアルデックが提供して

います。

HES Proto-AXI 動作モード

HES Proto-AXIは、次の2つの異なるモード動作します。

HES.Proto-AXI ブリッジモード: 主な機能

DUT 用の単一のAXI4 マスタインターフェイスと

デザインと通信するためのC-API を使用して、ホ • 高帯域、低遅延のホストブリッジ

ストからFPGA へのインターフェイスを提供しま • PC/ワークステーションホストからPCI

す。 これはPCIe 上のブリッジとして機能し、プ Express を介したAMBA AXI ブリッジ

ロトタイピングボード上のAXI ブリッジに接続し

• 組み込みホストからMGT を介したAMBA

ます。これによりプロトタイピングプロジェクト

AXI ブリッジ

をホストワークステーションに接続できます。

• 複数のAXI マスター/スレーブポートを搭載

したAMBA AXIインターコネクト

• メモリマップ管理用のアドレスリマッパー

• 割り込みとGPIOサポート

• ユーザースペースアプリケーションC/C ++

API およびPython ラッパー

• PC/ワークステーションホスト上のWindows

およびLinux OS のサポート

• TLM 2.0 インターフェースを備えたQEMU、

OVP、Renode などの仮想プラットフォーム

サポート

• オンボード周辺機器を使用するサンプルデ

ザイン

• ボードドキュメント

• FPGA およびPLL プログラミング

• ボードアクセスのロックと解除

Page2

スライド 2

HES.Proto-AXIインタコネクトモード:

ホストブリッジ機能を完全なAXI イン

ターコネクトと統合しました。完全な

AXI インターコネクトには、FPGA

チップ間の相互接続を含む複数デザイ

ンモジュールまたはアクセラレータ

カーネルを接続するため、複数のAXIマ

スタ/スレーブポートが組み込まれtてい

ます。また、DDR やRLD などの外部メ

モリモジュールへの高速アクセスも可

能です。

検証環境に合わせた2種類のホストブリッジ

幅広い用途に対応するために、HES Proto-AXI は2タイプ(ワークステーションホストまたは

組み込みホスト)のホストブリッジモジュールを提供しています

ワークステーションホスト 組み込みホスト

ワークステーション/PC からFPGAに実装された FPGA ボードに搭載されたXilinx Zynq 7000、

AXI デバイスへのブリッジです。FPGA ボードと またはMPSoC から、同じボード上の別FPGA

ワークステーション間の接続はPCI Express に に実装されたAXI デバイスへのブリッジです。

て物理的に接続されます。ホスト側のテストコン FPGA 間の接続は、Multi Gigabit Transceivers

トローラソフトウェアの迅速な開発のために (MGT)にて接続されます。テストコントロー

C/C++ API とPython ラッパー、PCI Express ラ組み込みアプリケーションの迅速な開発の

ドライバを提供します ためにソフトウェアスタック(C/C ++ API を

含む)を提供します

サポートボード名 動作モード FPGA チップ メモリ 周波数

HES7XV4000BPX_REV2 Bridge / - FPGA0*: XC7K325T-FBG900 (Kintex-7) - 4GB DDR3 KVR 1333D3S9/4G** (one slot) 125

Interconnect - FPGA1: XC7V2000TFFG1761 (Virtex7) - 8GB DDR3 KVR 1333D3S9/8G** MHz

- FPGA2: XC7V2000TFFG1761 (Virtex7) (optional, two slots)

HESXUS440 Bridge / - FPGA0*: XC7Z100-FFG900 (Zynq-7000) - 8GB DDR4 KVR21S15S8/8 (two slots) 161

Interconnect - FPGA1: XCVU440-A2892 (Virtex-UltraScale) - 16G DDR4 KVR21S15D8/16 (two slots) RFU MHz

- 64MB RLD MT44k32M18RB (two memories) RFU

HES-XCVU9P-XCZU7EV Bridge / - FPGA0*: XCZU7-FFVC1156 (Zynq-UltraScale+) - 8GB DDR4 KVR21S15S8/8 (two slots) 244.141

Interconnect - FPGA1: XCVU9P-FLGB2104 (Virtex-UltraScale+) - 16G DDR4 KVR21S15D8/16 (two slots) RFU MHz

- 64MB RLD MT44k32M18RB (two memories) RFU

HES-XCVU9P-QDR Bridge / - FPGA0****: XCVU9P-FLGB2104 - 3x 32MB MT44K32M18RB-107 250

Interconnect (Virtex-UltraScale+) MHz

HESXUS1320BPX Bridge - FPGA0*: XC7VX690-FFG1926 (Virtex-7) - Up to 48 GB of DDR4 161

- FPGA1***: XCVU440-A2892 (Virtex-UltraScale) - 6 DDR SODIMM Slots MHz

- FPGA2***: XCVU440-A2892 (Virtex-UltraScale) - 2 slots and up to 16 GB per FPGA

- FPGA3*****: XCVU440-A2892 (Virtex-UltraScale)

*) FPGA0 チップには制御モジュールが含まれており、ユーザーは使用できません。

**) FPGA0 では8GB DDR3 KVR 1333D3S9/8G メモリのみがサポートされています。

***) AXI インターフェイスのないFPGA。 ユーザーがそれを使用したい場合はFPGAチップとの通信チャネルを準備する必要があります。

****) FPGA チップには、HES.Proto-AXI コントロールモジュールとユーザーデザインの両方が含まれています。

*****)アルデックが提供するAXI4 インターフェイスを備えたFPGAチップ

アルデック・ジャパン株式会社

東京都新宿区西新宿3-3-13

西新宿水間ビル 6F

03-6693-4146

sales-jp@aldec.com

http://www.aldec.com/jp