1/1ページ

ダウンロード(760.9Kb)

FPGA設計・検証に最適な機能を搭載

【主な機能と利点】

◆プロジェクト管理

・チームベースの統一されたデザイン環境でローカルまたはリモート・チームにわたって統一性を維持可能

・設定可能なFPGA/EDAフロー・マネージャは120種類以上のベンダツールとインタフェースを取れるので、FPGA開発中一貫して1つのプラットフォームを使い続けられます

◆グラフィカル/テキスト・デザインエントリ

・テキスト、スケマティックおよびステートマシンを活用してデザインを素早く作成

・セキュアで信頼性の高い相互利用可能な暗号化規格でIPを配布・送付

◆シミュレーションとデバッギング

・共通カーネルの強力なVHDL/Verilog/SystemVerilog(Design)/SystemC対応混合言語シミュレータ

・GUIで操作可能なデバッギングとコード高品質化ツールでコードの品質と信頼性を確保

・コードカバレッジ解析ツールで測定基準に基づく検証を実施、デザインの実行されない部分を特定

・アサーションベース検証(SVA, PSL, OVA)で検証の質をアップ、より多くのバグを発見

・HDLシミュレーションとDSPブロック用の高抽象度数学モデル環境のギャップはMATLAB/Simulinkインタフェースで埋めます

◆HTML/PDFドキュメンテーション

・HDL-スケマティックコンバータでデザインの核心部分を抜き出し分かりやすいグラフィックで表現

・デザインドキュメントをHTMLやPDFで自動生成、すぐにデザインを共有可能

関連メディア

このカタログについて

| ドキュメント名 | FPGA開発統合環境 Active-HDL |

|---|---|

| ドキュメント種別 | 製品カタログ |

| ファイルサイズ | 760.9Kb |

| 登録カテゴリ | |

| 取り扱い企業 | アルデック・ジャパン株式会社 (この企業の取り扱いカタログ一覧) |

この企業の関連カタログ

このカタログの内容

Page1

スライド 1

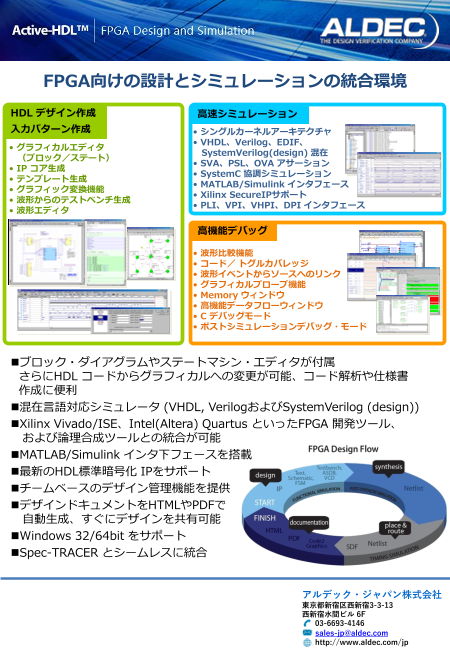

FPGA向けの設計とシミュレーションの統合環境

HDL デザイン作成 高速シミュレーション

入力パターン作成 • シングルカーネルアーキテクチャ

• VHDL、Verilog、EDIF、

• グラフィカルエディタ

SystemVerilog(design) 混在

(ブロック/ステート)

• SVA、PSL、OVA アサーション

• IP コア生成

• SystemC 協調シミュレーション

• テンプレート生成

• MATLAB/Simulink インタフェース

• グラフィック変換機能

• Xilinx SecureIPサポート

• 波形からのテストベンチ生成

• PLI、VPI、VHPI、DPI インタフェース

• 波形エディタ

高機能デバッグ

• 波形比較機能

• コード/ トグルカバレッジ

• 波形イベントからソースへのリンク

• グラフィカルプローブ機能

• Memory ウィンドウ

• 高機能データフローウィンドウ

• C デバッグモード

• ポストシミュレーションデバッグ・モード

◼ブロック・ダイアグラムやステートマシン・エディタが付属

さらにHDL コードからグラフィカルへの変更が可能、コード解析や仕様書

作成に便利

◼混在言語対応シミュレータ (VHDL, VerilogおよびSystemVerilog (design))

◼Xilinx Vivado/ISE、Intel(Altera) Quartus といったFPGA 開発ツール、

および論理合成ツールとの統合が可能

◼MATLAB/Simulink インタ下フェースを搭載

◼最新のHDL標準暗号化 IPをサポート

◼チームベースのデザイン管理機能を提供

◼デザインドキュメントをHTMLやPDFで

自動生成、すぐにデザインを共有可能

◼Windows 32/64bit をサポート

◼Spec-TRACER とシームレスに統合

アルデック・ジャパン株式会社

東京都新宿区西新宿3-3-13

西新宿水間ビル 6F

03-6693-4146

sales-jp@aldec.com

http://www.aldec.com/jp