1/2ページ

ダウンロード(932.3Kb)

Riviera-PRO™は、次世代の最先端FPGAやSoCを制作するエンジニアの検証ニーズに対応します。テストベンチ生産性の最大化、再利用、高性能シミュレーション・エンジンとデバッグ機能を様々な抽象レベルで統合することによる自動化、さらには最新言語と検証ライブラリ規格のサポートなどが、Riviera-PROで実現できます。

関連メディア

このカタログについて

| ドキュメント名 | 高速RTLシミュレータ『Riviera-PRO』 |

|---|---|

| ドキュメント種別 | 製品カタログ |

| ファイルサイズ | 932.3Kb |

| 登録カテゴリ | |

| 取り扱い企業 | アルデック・ジャパン株式会社 (この企業の取り扱いカタログ一覧) |

この企業の関連カタログ

このカタログの内容

Page1

スライド 1

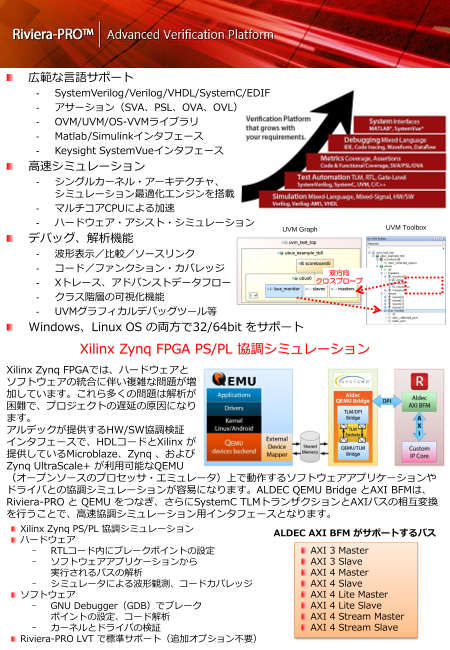

広範な言語サポート

- SystemVerilog/Verilog/VHDL/SystemC/EDIF

- アサーション(SVA、PSL、OVA、OVL)

- OVM/UVM/OS-VVMライブラリ

- Matlab/Simulinkインタフェース

- Keysight SystemVueインタフェース

高速シミュレーション

- シングルカーネル・アーキテクチャ、

シミュレーション最適化エンジンを搭載

- マルチコアCPUによる加速

- ハードウェア・アシスト・シミュレーション

UVM Graph UVM Toolbox

デバッグ、解析機能

- 波形表示/比較/ソースリンク

- コード/ファンクション・カバレッジ

双方向

- Xトレース、アドバンストデータフロー クロスプローブ

- クラス階層の可視化機能

- UVMグラフィカルデバッグツール等

Windows、Linux OS の両方で32/64bit をサポート

Xilinx Zynq FPGA PS/PL 協調シミュレーション

Xilinx Zynq FPGAでは、ハードウェアと

ソフトウェアの統合に伴い複雑な問題が増

加しています。これら多くの問題は解析が

困難で、プロジェクトの遅延の原因になり

ます。

アルデックが提供するHW/SW協調検証

インタフェースで、HDLコードとXilinx が

提供しているMicroblaze、Zynq 、および

Zynq UltraScale+ が利用可能なQEMU

(オープンソースのプロセッサ・エミュレータ)上で動作するソフトウェアアプリケーションや

ドライバとの協調シミュレーションが容易になります。ALDEC QEMU Bridge とAXI BFMは、

Riviera-PRO と QEMU をつなぎ、さらにSystemC TLMトランザクションとAXIバスの相互変換

を行うことで、高速協調シミュレーション用インタフェースとなります。

Xilinx Zynq PS/PL 協調シミュレーション ALDEC AXI BFM がサポートするバス

ハードウェア

- RTLコード内にブレークポイントの設定 AXI 3 Master

- ソフトウェアアプリケーションから AXI 3 Slave

実行されるパスの解析 AXI 4 Master

- シミュレータによる波形観測、コードカバレッジ AXI 4 Slave

ソフトウェア AXI 4 Lite Master

- GNU Debugger(GDB)でブレーク AXI 4 Lite Slave

ポイントの設定、コード解析 AXI 4 Stream Master

- カーネルとドライバの検証 AXI 4 Stream Slave

Riviera-PRO LVT で標準サポート(追加オプション不要)

Page2

スライド 2

クリティカルセーフティデザインには

コードカバレッジ収集が必須

自動車、医療機器、航空産業など、クリティカルセーフティデザイン

ではコードカバレッジによる検証の網羅性の確認は重要

検証抜けは重大事故の原因になりかねない

コンプライアンスの承認を得られない

コードカバレッジは、もともとソフト

ウェアの検証手法の一つで、検証に

おけるソースコードの網羅性を数値化

ソースコードのどこを検証したか

検証抜けはないか

該当行が何回実行されたか

検証不足によるバグの発生を未然に防ぐ

Riviera-PRO のコードカバレッジ

シミュレーションエンジンにカバレッジ機能を統合

ランタイム時間への影響は最小

ソースコードへの追加記述は不要

ソースコードと結果を同一画面で

表示

カバレッジの詳細の表示

Accellera の統一カバレッジ・

データベース (UCIS)互換の

カバレッジデータベース

複数のカバレッジ結果をマージ

各種カバレッジタイプをサポート

ステートメントカバレッジ トグルカバレッジ

ソースコードのライン毎に何回実行 信号値が 0⇔1 の変化した回数をカウント

されたかをカウント パスカバレッジ(VHDLのみ)

ブランチカバレッジ 依存する条件文間の組合せ

分岐条件の実行状況をカウント ステートマシンカバレッジ

エクスプレッションカバレッジ ステート/トランジッションの実行数、

代入されている値を持つ式内の およびステートの実行順序が確認可能

変数の組み合わせ

コンディションカバレッジ

条件内の変数や条件の組み合わせ

アルデック・ジャパン株式会社

東京都新宿区西新宿3-3-13

西新宿水間ビル 6F

03-6693-4146

sales-jp@aldec.com

http://www.aldec.com/jp