1/2ページ

ダウンロード(957.7Kb)

Windows/Linuxで動作可能なスタティックデザイン解析ツール

『ALINT-PRO』は、コーディングスタイルと命名規則、RTLと合成結果のシミュレーション不一致、スムーズで最適な合成、正しいFSM記述、 設計の後工程での問題、クロックおよびリセットツリーの問題、CDC、RDC、DFT、およびポータビリティと再利用のためのコーディングなどを中心に、VHDL、Verilog、SystemVerilogで記述されたRTLコードを解析する検証ソリューションです。

関連メディア

このカタログについて

| ドキュメント名 | RTLコード解析・検証ソリューション ALINT-PRO |

|---|---|

| ドキュメント種別 | 製品カタログ |

| ファイルサイズ | 957.7Kb |

| 登録カテゴリ | |

| 取り扱い企業 | アルデック・ジャパン株式会社 (この企業の取り扱いカタログ一覧) |

この企業の関連カタログ

このカタログの内容

Page1

スライド 1

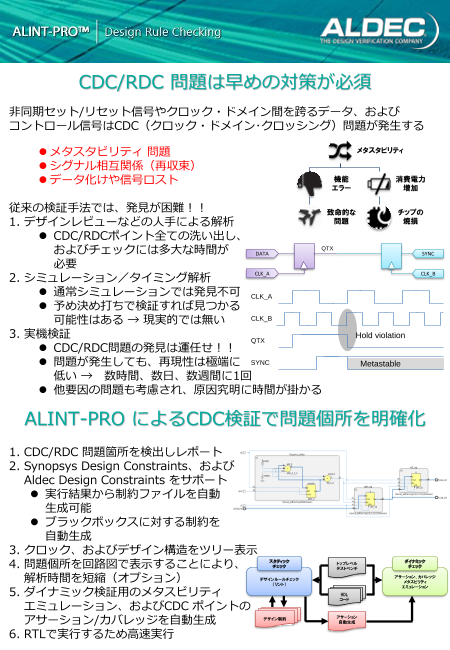

CDC/RDC 問題は早めの対策が必須

非同期セット/リセット信号やクロック・ドメイン間を跨るデータ、および

コントロール信号はCDC(クロック・ドメイン・クロッシング)問題が発生する

⚫メタスタビリティ 問題 メタスタビリティ

⚫シグナル相互関係(再収束)

⚫データ化けや信号ロスト 機能 消費電力

エラー 増加

従来の検証手法では、発見が困難!! 致命的な チップの

1. デザインレビューなどの人手による解析 問題 焼損

⚫ CDC/RDCポイント全ての洗い出し、

およびチェックには多大な時間が QTX

DATA SYNC

必要

CLK_A CLK_B

2. シミュレーション/タイミング解析

⚫ 通常シミュレーションでは発見不可 CLK_A

⚫ 予め決め打ちで検証すれば見つかる

可能性はある → 現実的では無い CLK_B

3. 実機検証 Hold violation

QTX

⚫ CDC/RDC問題の発見は運任せ!!

⚫ 問題が発生しても、再現性は極端に SYNC Metastable

低い → 数時間、数日、数週間に1回

⚫ 他要因の問題も考慮され、原因究明に時間が掛かる

ALINT-PRO によるCDC検証で問題個所を明確化

1. CDC/RDC 問題箇所を検出しレポート

2. Synopsys Design Constraints、および

Aldec Design Constraints をサポート

⚫ 実行結果から制約ファイルを自動

生成可能

⚫ ブラックボックスに対する制約を

自動生成

3. クロック、およびデザイン構造をツリー表示

4. 問題個所を回路図で表示することにより、 スタティック ダイナミック

トップレベル

チェック チェック

テストベンチ

解析時間を短縮(オプション) アサーション、カバレッジ

デザインルールチェック

メタスビリティ

(リント)

エミュレーション

5. ダイナミック検証用のメタスビリティ HDL

コード

エミュレーション、およびCDC ポイントの

アサーション/カバレッジを自動生成 デザイン制約 アサーション

自動生成

6. RTLで実行するため高速実行

Page2

スライド 2

評価ボード、実機では動作しない

シミュレーションで見つからない問題

⚫シミュレーションと論理合成のミスマッチ

⚫言語仕様では問題ないが、論理合成に不向きなデザイン

⚫意図していないラッチやループ回路

⚫デザイン一部の初期化抜け

⚫ If/case 文の深いネスト module detector( CLK, RST_X, DATA, DOUT );

input RST_X, CLK;

input [3:0] DATA;

⚫ FSMで到達できないステート output reg DOUT;

reg [3:0] Y;

always @( DATA ) begin

case( DATA )

0: Y = 4'b1111;

この様な記述の問題は、実機検証で多大な時間を要する 1: Y = 4'b1110;

2: Y = 4'b1100;

問題を発生する。さらに解析箇所を絞り込むことは容易 3: Y = 4'b1011;

default: Y = 4'bxxxx;

endcase

ではない end

always @( posedge CLK or negedge RST_X ) begin

⚫電源の不安定? if( !RST_X )

DOUT <= 1'b0;

else if( Y[0] == 1'b1 )

⚫タイミング不良? DOUT <= 1'b1;

else

DOUT <= 1'b0;

⚫デザインバグ? end

endmodule

⚫周辺回路の影響?

⚫ CDC/RDC問題?

ALINT-PRO は後工程で問題となる個所を早期に明確化

1. ALINT-PRO は、RTL コードを解析する検証ソリューション

⚫クロック・リセット・ネットワークの解析

⚫ RTLシミュレーションと合成後シミュレーションの

ミスマッチを防止

⚫コードのポータビリティと再利用性

⚫ ALDEC_CDCルール・プラグインによる幅広い

CDC/RDCチェック

⚫ IP記述用のデザイン制約拡張

2. デザイン・フローの早期にバグを検出:

⚫デザイン作成/変更時、およびシミュレーション前に実行

3. 業界最先端の設計手法に基づいた包括的なルールライブラリ

⚫ STARC‐半導体理工学センターが設定したルール

⚫ Aldec SystemVerilog/Premium, RMM, DO-254 ルールなど

4. 解析と修正を用意にする多彩な解析ウィンドウとレポート

5. FPGAベンダの基本ライブラリをサポート

6. ベンダツール(Xilinx, Altera)の

プロジェクトからのコンバートをサポート

7. Windows、Linux OS の両方で32/64bit を

サポート

アルデック・ジャパン株式会社

東京都新宿区西新宿3-3-13

西新宿水間ビル 6F

03-6693-4146

sales-jp@aldec.com

http://www.aldec.com/jp