1/7ページ

ダウンロード

ミリ波を使用するイメージング技術は、セキュリティを確保するための手段として広く活用されています。例えば、空港、公共施設、スタジアムで使われるスキャナに適用すれば大きなメリットが得られます。

ミリ波対応のスキャナであれば、金属と非金属の両方の危険物を検知/特定することが可能です。つまり、従来の金属探知機と比べて明らかに勝る機能を実現することができます。本稿では、まずミリ波イメージングを実現するハードウェアの仕組みについて説明します。その上で、エッジにおける処理をベースとすることで、膨大なデータによって生じる負荷の管理を可能にするチップセットを紹介します。それらの製品を採用すれば、セキュリティの確保を目的として使用されるウォークスルー方式のスキャン・システムを開発することが可能になります。

このカタログについて

| ドキュメント名 | エッジ処理をベースとするミリ波対応のセキュリティ用スキャナを実現する |

|---|---|

| ドキュメント種別 | ホワイトペーパー |

| 取り扱い企業 | アナログ・デバイセズ株式会社 (この企業の取り扱いカタログ一覧) |

この企業の関連カタログ

このカタログの内容

Page1

Vol 57, No 2—April 2023

エッジ処理をベースとするミリ波対応の

セキュリティ用スキャナを実現する

著者:Eamon Nash、アプリケーション・エンジニアリング・ディレクタ

はじめに

ミリ波(mmWave)を使用するイメージング技術(以下、ミリ Rx Rx

波イメージング)は、セキュリティを確保するための手段として Tx Tx

広く活用されています。例えば、空港、公共施設、スタジアムで Rx Rx

Tx Tx

使われるスキャナに適用すれば大きなメリットが得られます。ミ

Rx Rx

リ波対応のスキャナであれば、金属と非金属の両方の危険物を検

Tx Tx

知/特定することが可能だからです。つまり、従来の金属探知機

Rx Rx

と比べて明らかに勝る機能を実現することができます。本稿では、 Tx Tx

まずミリ波イメージングを実現するハードウェアの仕組みについ Rx Rx

て説明します。その上で、エッジにおける処理をベースとするこ

とで、膨大なデータによって生じる負荷の管理を可能にするチッ 図1. ミリ波イメージングをベースとする

プセットを紹介します。それらの製品を採用すれば、セキュリ スキャナ・システム

ティの確保を目的として使用されるウォークスルー方式のスキャ

RF信号の透過の深さと反射の性質は周波数によって異なります。

ン・システムを開発することが可能になります。

そのため、上記のスキャン処理は広帯域にわたる複数の周波数を

使って繰り返されます。その結果として得られるベクトル行列は、

ミリ波イメージングの仕組み (周波数と空間的な位置に対する)多次元アレイになります。そ

図1は、ミリ波イメージングをベースとするスキャナの概要を示 れを使用して画像を生成することにより、重ね着した衣服の中に

したものです。このスキャナは、トランスミッタとレシーバーの 隠れた金属/非金属を検知することが可能になります。

アレイを搭載しています。それらは、いずれも空間的に分散配備

されたアンテナ・アレイに接続されています。この構造は、リター このようなスキャン処理を実行するためのハードウェアは、複数

ン・ロスやS11の測定に使用されるネットワーク・アナライザに のチャンネルを備えており、広い動作周波数範囲に対応している

似ています。このシステムでは、アレイ内の1つのアンテナから 必要があります。10GHz~40GHzの周波数を使用できれば、セ

単一周波数、小振幅の信号が継続的に出力されます。その信号が キュリティ用のスキャナで一般的に対象とする物(衣類、リュッ

対象物(人や物)で反射することにより、後方散乱が生成されま ク、凶器、爆発物)を十分に区別することができます。また、チャ

す。図1の例では、単一の点からの反射信号を示してあります。 ンネル数が多いシステムほど分解能は高くなる傾向があり、小さ

実際には、アンテナから出力される信号は無指向性なので、対象 な物体でも検知することが可能になります。例えば、空港で使用

物の複数の点から反射が生じます。 されるスキャナの場合、かみそりの刃を検出できることは重要で

す。一方、公共施設やスタジアムでは、凶器や爆発物など、より

後方散乱が生成されると、アレイを構成するすべての受信アンテ 大きな物体の検出に重点が置かれます。一般に、後者の用途では

ナによってその振幅と位相が測定されます。なお、送信信号から チャンネル数の少ないシステムが使用されます。

受信信号への直接的なリークを低減するために、送信アンテナと

受信アンテナの間では偏波が用いられることがあります。振幅と

位相の測定が完了したら、(同じ周波数で動作する)別の送信ア

ンテナから同じ信号が送信され、後方散乱の振幅と位相を測定す

る処理が繰り返されます。

VISIT ANALOG.COM/JP

1 エッジ処理をベースとするミリ波対応のセキュリティ用スキャナを実現する

Page2

+12 V パワー・マネージメント

LTM4643 LTM4367 LTM4643

µModule® 降圧レギュ 降圧レギュ

LT3045 LT8640 LT8640 LT3088 LT3045 レータ レータ

LDO Silent Switcher® Silent Switcher LDO LDO

2.5 V

2.5 V 2.5 V

2.5A VDAR2001 2.5 V

10- ADAR2001 1.0 V A 1.0 V D 1.8 V D 1.8 VA 1.0 V D 1.8 V D

10-2.A5D VAR2001 2.5 V 2.5VADAR2004

120.-5A4VD0A GRH2z0

ADAR2001 2.5 V R0x4 Mixer

10-A4D0A GRH2zA0 RD0xA4 RM2ix0e0r

10A-4D0A GRH20z 0R4x Mixer 4 AD9083

1100G- Hz~40GHzの 10GHz~40GHzの1ク0-ワ4ッ0 GドHRzx ミRxキ Mサixーer 16チャンネルのCTSD ADC

周波数逓4倍X PA

器×4

M4uX PA

ltiplier

M4uXlti PA ADC DDC

&plier

周M波ul数tip& PA

Fliileter r PA

3.3 V 5 V 逓倍器&Fとilter PA JESD

ADF4368 フィルFタilt×er PA

4 ADC DDC

PA 204B

PLL/VCO PA FPGA

2.5GHz~ Fast PA

10GHz SFeaqsutencerPA

SFeaqsutencer ADC DDC

PA

S高eq速uencer PA

PA SYSREF

シーケンADサV RESPEPATA ADC DDC

ADV RESET 4X

M4uX

ADV RESET ltiplier Fast

M4uX CLK

ADV RESET lti&plie4r

周波数 X SFeaqsutencer

Multi&FpilMliteeurrltipliSeFeraqsutenFcaesr逓倍&器 t

Filとter & Se 高速

フィルタ×4 シーquケeンnFilter Sceサeqruencer ADC DDC

Filter シーケンサの

SYSREF CLK 制御

LOIN ADV RESET

2.5GHz~10GHz

4線式SPI(SCLK、CS、SDIO、SDO)

LT3045 5 V ADF4368

LDO 3.3 V PLL/VCO

FREF ADC ADC

ADP5052 5 V SYSREF CLK FPGA

降圧レギュ SYSREF

3.3 V AD9528

レータ クロック・ジェネレータ FPGA

FREF CLK

図2. ミリ波イメージングをベースとする

スキャナの全体像

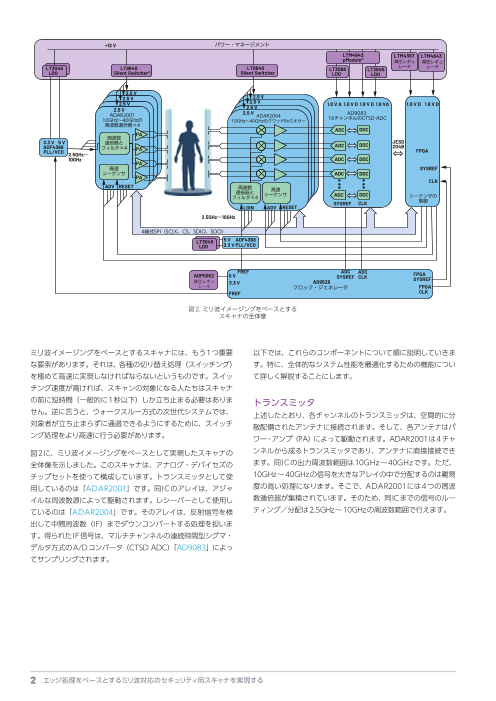

ミリ波イメージングをベースとするスキャナには、もう1つ重要 以下では、これらのコンポーネントについて順に説明していきま

な要素があります。それは、各種の切り替え処理(スイッチング) す。特に、全体的なシステム性能を最適化するための機能につい

を極めて高速に実現しなければならないというものです。スイッ て詳しく解説することにします。

チング速度が高ければ、スキャンの対象になる人たちはスキャナ

の前に短時間(一般的に1秒以下)しか立ち止まる必要はありま トランスミッタ

せん。逆に言うと、ウォークスルー方式の次世代システムでは、 上述したとおり、各チャンネルのトランスミッタは、空間的に分

対象者が立ち止まらずに通過できるようにするために、スイッチ 散配備されたアンテナに接続されます。そして、各アンテナはパ

ング処理をより高速に行う必要があります。 ワー・アンプ(PA)によって駆動されます。ADAR2001は4チャ

図2に、ミリ波イメージングをベースとして実現したスキャナの ンネルから成るトランスミッタであり、アンテナに直接接続でき

全体像を示しました。このスキャナは、アナログ・デバイセズの ます。同ICの出力周波数範囲は10GHz~40GHzです。ただ、

チップセットを使って構成しています。トランスミッタとして使 10GHz~40GHzの信号を大きなアレイの中で分配するのは難易

用しているのは「ADAR2001」です。同ICのアレイは、アジャ 度の高い処理になります。そこで、ADAR2001には4つの周波

イルな周波数源によって駆動されます。レシーバーとして使用し 数逓倍器が集積されています。そのため、同ICまでの信号のルー

ているのは「ADAR2004」です。そのアレイは、反射信号を検 ティング/分配は2.5GHz~10GHzの周波数範囲で行えます。

出して中間周波数(IF)までダウンコンバートする処理を担いま

す。得られたIF信号は、マルチチャンネルの連続時間型シグマ・

デルタ方式のA/Dコンバータ(CTSD ADC)「AD9083」によっ

てサンプリングされます。

2 エッジ処理をベースとするミリ波対応のセキュリティ用スキャナを実現する

Page3

ADAR2001

周波数逓倍器/フィルタ トランスミッタ

×4 PA RFOUT1+

RFOUT1–

RFIN バッファ ×4

×4 RFOUT2+

PA RFOUT2–

PA RFOUT3+

CS RFOUT3–

SDIO SPI

SCLK 制御

SDO RFOUT4+

PA RFOUT4–

温度

センサー

周波数逓倍器/フィルタ トランスミッタ ADC

ステート・マシン ステート・マシン

(16の状態) (70の状態)

MRST MADV TxRST TxADV

図3. ADAR2001の内部ブロック図

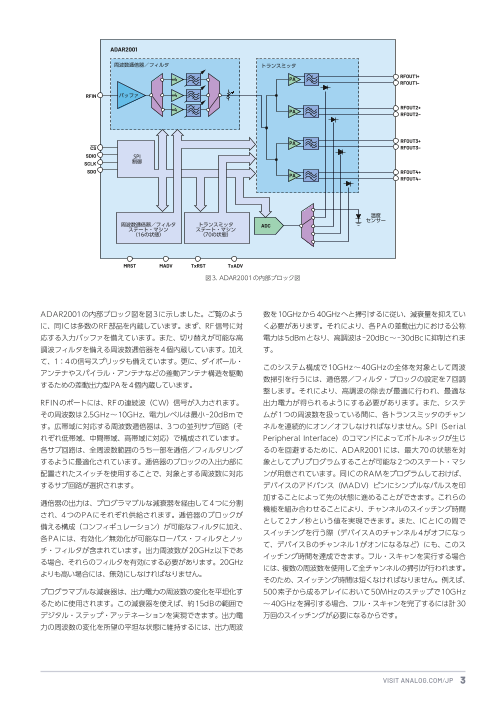

ADAR2001の内部ブロック図を図3に示しました。ご覧のよう 数を10GHzから40GHzへと掃引するに従い、減衰量を抑えてい

に、同ICは多数のRF部品を内蔵しています。まず、RF信号に対 く必要があります。それにより、各PAの差動出力における公称

応する入力バッファを備えています。また、切り替えが可能な高 電力は5dBmとなり、高調波は-20dBc~-30dBcに抑制されま

調波フィルタを備える周波数逓倍器を4個内蔵しています。加え す。

て、1:4の信号スプリッタも備えています。更に、ダイポール・

このシステム構成で10GHz~40GHzの全体を対象として周波

アンテナやスパイラル・アンテナなどの差動アンテナ構造を駆動

数掃引を行うには、逓倍器/フィルタ・ブロックの設定を7回調

するための差動出力型PAを4個内蔵しています。

整します。それにより、高調波の除去が最適に行われ、最適な

RFINのポートには、RFの連続波(CW)信号が入力されます。 出力電力が得られるようにする必要があります。また、システ

その周波数は2.5GHz~10GHz、電力レベルは最小-20dBmで ムが1つの周波数を扱っている間に、各トランスミッタのチャン

す。広帯域に対応する周波数逓倍器は、3つの並列サブ回路(そ ネルを連続的にオン/オフしなければなりません。SPI(Serial

れぞれ低帯域、中間帯域、高帯域に対応)で構成されています。 Peripheral Interface)のコマンドによってボトルネックが生じ

各サブ回路は、全周波数範囲のうち一部を逓倍/フィルタリング るのを回避するために、ADAR2001には、最大70の状態を対

するように最適化されています。逓倍器のブロックの入出力部に 象としてプリプログラムすることが可能な2つのステート・マシ

配置されたスイッチを使用することで、対象とする周波数に対応 ンが用意されています。同ICのRAMをプログラムしておけば、

するサブ回路が選択されます。 デバイスのアドバンス(MADV)ピンにシンプルなパルスを印

加することによって先の状態に進めることができます。これらの

逓倍器の出力は、プログラマブルな減衰器を経由して4つに分割

機能を組み合わせることにより、チャンネルのスイッチング時間

され、4つのPAにそれぞれ供給されます。逓倍器のブロックが

として2ナノ秒という値を実現できます。また、ICとICの間で

備える構成(コンフィギュレーション)が可能なフィルタに加え、

スイッチングを行う際(デバイスAのチャンネル4がオフになっ

各PAには、有効化/無効化が可能なローパス・フィルタとノッ

て、デバイスBのチャンネル1がオンになるなど)にも、このス

チ・フィルタが含まれています。出力周波数が20GHz以下であ

イッチング時間を達成できます。フル・スキャンを実行する場合

る場合、それらのフィルタを有効にする必要があります。20GHz

には、複数の周波数を使用して全チャンネルの掃引が行われます。

よりも高い場合には、無効にしなければなりません。

そのため、スイッチング時間は短くなければなりません。例えば、

プログラマブルな減衰器は、出力電力の周波数の変化を平坦化す 500素子から成るアレイにおいて50MHzのステップで10GHz

るために使用されます。この減衰器を使えば、約15dBの範囲で ~40GHzを掃引する場合、フル・スキャンを完了するには計30

デジタル・ステップ・アッテネーションを実現できます。出力電 万回のスイッチングが必要になるからです。

力の周波数の変化を所望の平坦な状態に維持するには、出力周波

VISIT ANALOG.COM/JP 3

Page4

ADAR2004

レシーバー

RFIN1+ IFOUT1+

LNA VGA

RFIN1– IFOUT1–

RFIN2+ IFOUT2+

LNA VGA

RFIN2– IFOUT2–

RFIN3+

LNA VGA IFOUT3+

RFIN3– IFOUT3–

RFIN4+ LNA VGA IFOUT4+

RFIN4– IFOUT4–

周波数逓倍器/フィルタ

×4

LOIN バッファ ×4

×4

CS

SDIO SPI ADC

SCLK 制御

SDO 温度

センサー

周波数逓倍器/フィルタ レシーバー

ステート・マシン ステート・マシン

(16の状態) (16の状態)

MRST MADV RxRST RxADV

図4. ADAR2004の内部ブロック図

各チャンネルのRF出力は、オンチップの各RFディテクタによっ 用意されており、2つ目のPLLによって駆動されます。このPLL

てモニタリングできます。ダイの温度も、オンチップの温度セ の出力周波数は、ミキサーによって実数のIF出力が生成される

ンサーによってモニタリングすることが可能です。これらのセン ように、無線周波数にオフセットを加えた値になっています。ミ

サーの出力は、5:1のアナログ・マルチプレクサに送信されます。 キサーのIF出力は、AD9083(CTSD ADC)によってサンプリ

マルチプレクサは、オンチップの8ビットADCに必要な信号を ングされます。同ICは16チャンネルの製品であり、デジタル・

引き渡します。 ダウン・コンバータを内蔵しています。また、ゼロIFのアーキテ

クチャではなくIFサンプリングのアーキテクチャを採用していま

フェーズ・ロック・ループ/電圧制御発振器(PLL/VCO)であ

す。その理由は、レシーバー内のLOリークに起因するDCオフ

る「ADF4368」は、トランスミッタの回路にスティミュラス

セットと、LOの直交スプリッタ内の直交バランスが完璧でない

を供給します。その出力信号は、送信チャンネルの数に応じて

ことに起因するI/Qの誤差を防ぎたいからです。これらの問題は、

複数回分割されます。同ICの比較的高い出力電力(9dBm)と

キャリブレーションによって軽減することも可能です。しかし、

ADAR2001の最小入力閾値(-20dBm)により、ADF4368の

LOリークと直交誤差は周波数によって異なる傾向があるため、

出力は、バッファ・アンプを使用することなく何度もパッシブに

入力周波数ごとにキャリブレーションを実行しなければならなく

分割することができます。

なります。

レシーバー 図4は、ADAR2004の内部ブロック図です。LOINに入力さ

トランスミッタによって送信された信号は対象物で反射します。 れた2.5GHz~10GHzの正弦波は、逓倍器によって10GHz~

その反射信号を受信するのがレシーバーです。レシーバーは、マ 40GHzの信号に変換されます。逓倍器の出力は、IF出力に対す

ルチチャンネルのミキサーとADCのアレイとして構成されます。 るプログラマブル・ゲイン機能を備える4つのミキサーに引き渡

ADAR2004は、クワッドミキサーとADC用ドライバの機能を併 されます。トランスミッタであるADAR2001と同様に、レシー

せ持ちます。また、デジタル制御ゲイン・アンプ(DGA)も内 バーであるADAR2004も、プリプログラムが可能な2つのス

蔵しています。局部発振器(LO)の入力部には4つの逓倍器が テート・マシンを内蔵しています。

4 エッジ処理をベースとするミリ波対応のセキュリティ用スキャナを実現する

Page5

AVDD AVDD1P8 DVDD DVDD1P8

(1 V) (1.8 V) (1 V) (1.8 V)

AD9083

NCO0 NCO1 NCO2

Jによるデシ

メーション ゲイン

VIN1+~ ミキサー

VIN16+

ADC 平均化/デシメー

VIN1-~ SERDOUT0±

CICデシメータ ション・フィルタ

VIN16- JESD204B SERDOUT1±

出力 SERDOUT2±

ミキサー 平均化/デシメー

ション・フィルタ ゲイン SERDOUT3±

ミキサー 平均化/デシメー SYNCINB±

ション・フィルタ ゲイン

16チャンネル

CLK± PLL、JESD204Bの CSB

SYSREF± サブクラス1の制御、 SPI、 SCLK

TRIG± クロックの分配 制御レジスタ

SDIO

AGND DGND PD/STBY

図5. AD9083の内部ブロック図

マルチチャンネルのADC 各ADCは、帯域外にシェーピングされたΣΔ ADCからのノイ

図5は、AD9083(CTSD ADC)の内部ブロック図です。同 ズをフィルタで除去し、サンプル・レートを低下させるための

ADCの入力部は、ADAR2004(レシーバー)のIF出力と同じコ 信号処理回路を備えています。具体的には、CIC(Cascaded

モンモード電圧を使用するように設計されています。そのため、 Integrator Comb)フィル タ、複 数 のFIR(Finite Input

ミキサーの出力とADCの入力を直接接続することができます。 Response)型デシメーション・フィルタ(Jブロックによるデシ

ACカップリング・コンデンサを使用しないので、ミキサーの出 メーション)を備える直交デジタル・ダウン・コンバータ(DDC)、

力が急に切り替わっても(ミキサーの入力における周波数ステッ データ・ゲーティング・アプリケーション用の平均化デシメー

プが発生する際など)、充放電によるトランジェントが生じない ション・フィルタを備える最大3つの直交DDCチャンネルを実

ことが保証されます。 現する回路を内蔵しています。3つの直交DDCチャンネルを使

用すれば、最大3つの周波数を同時に復調することが可能です。

AD9083は、単極フィルタを備える1次CTSD ADCのアーキテ

それにより、スキャン時間を劇的に短縮できます(後述)。

クチャを採用しています。そのため、必要な外付けフィルタは最

小限で済み、プリント回路基板上の実装面積を削減できます。ま

た、このアーキテクチャでは、信号のセトリング時間を、ナイキ システムの設定と動作

スト・レートのADCのセトリング時間よりも短縮することがで ADAR2001とADAR2004は、大規模なアレイを構成した場合

きます。ナイキスト・レートのADCの場合、折り返し成分を除 に効率的な動作が得られるように設計されています。特に重視さ

去するために、選択性がかなり高いアンチエイリアシング(折返 れたのは、ワイヤリングによるオーバーヘッドを低減することで

し誤差防止)フィルタが必要になります。本稿で取り上げている す。ADAR2001/ADAR2004のRFIN、LOINの各入力ポートは、

アプリケーションでは、セトリング時間が短いことは重要な要件 最小-20dBmの入力レベルに対応します。これらの入力は共通

です。ADCのセトリング時間を、送信側のチャンネルのスイッ のLO源(本稿の例ではADF4368)で駆動できると望ましいで

チングに要するわずかな時間に適合させなければならないからで しょう。ADAR2001/ADAR2004の入力感度は、信号を増幅し

す。 なくても多数のパッシブなファンアウトが得られるというメリッ

トをもたらします。例えば、ウィルキンソン・パワー・スプリッ

タの純損失が1dBだとすると、ADF4368の9dBmの出力電力

によってパッシブなファンアウトに7回対応でき、128個のデバ

イス(512チャンネル)を駆動できることになります。

VISIT ANALOG.COM/JP 5

Page6

各ADAR2001の番号

送信の状態 動作

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

(リセット) SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP すべて

スリープ

0

1 CH1 SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP RDY IC 1が

2 CH2 SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP 送信

3 CH3 SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP

4 CH4 RDY SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP

5 RDY CH1 SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP IC 2が

6 SLP CH2 SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP 送信

7 SLP CH3 SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP

8 SLP CH4 RDY SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP

9 SLP RDY CH1 SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP IC 3が

送信

∙ ∙ ∙ ∙ ∙ ∙ ∙ ∙ ∙ ∙ ∙ ∙ ∙ ∙ ∙ ∙ ∙

∙ ∙ ∙ ∙ ∙ ∙ ∙ ∙ ∙ ∙ ∙ ∙ ∙ ∙ ∙ ∙ ∙

60 SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP CH4 RDY

61 SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP RDY CH1 IC 16が

62 SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP CH2 送信

63 SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP CH3

64 RDY SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP SLP CH4

図6. 16個のADAR2001のプログラミング。

1つのアドバンス・パルスによって駆動される掃引チャンネルの状態を示しています。

また、ADAR2001/ADAR2004が内蔵するシーケンサは、アド 図6を見ると、各ICには65個の状態があることがわかります。

バンス・ピンとリセット・ピンによって駆動されます。それらは、 そして、ほとんどのICはほとんどの時間、スリーブ・モード(SLP)

並列で駆動できるように設計されています。その目的は、駆動に になるようにプログラムされています。例えば、IC 1が完全にア

必要なプロセッサ/FPGAのGPIOの本数をできるだけ少なく抑 クティブになるのは、同ICのチャンネル1、2、3、4が順に送信

えることです。シーケンサに十分な深さと複雑さを持たせること を行う最初の4つの状態だけです。この4つの状態の間、それ以

で、1組のアドバンス・パルスとリセット・パルスによって最大 外のICはすべてSLPまたはレディ・モード(RDY)に設定されて

16個のADAR2001を駆動できます。 います。同様に、IC 2が完全にアクティブになるのは状態5~8

だけです。その間、他のICはすべてSLPまたはRDYに設定され

ADAR2001/ADAR2004を使用する場合、シーケンサのプログ

ています。このように、16個のステート・マシンが順にアクティ

ラミングを事前に行っておかなければなりません。両デバイスの

ブになるよう設定することにより、16個すべてのデバイスのアド

すべての機能には、SPIのコマンドを使用することでアクセスで

バンス・ラインとリセット・ラインを並列パルスによって駆動す

きます。但し、それに伴う遅延によって、全体的なスキャン時間

ることができます。

が許容できないほど長くなってしまいます。

ここで、RDYというのは、電力を節約しつつスイッチング時間

以下では、チャンネル・ベースのスキャンに向けて、64チャン

を最適化するために開発された中間状態です。ほとんどのトラ

ネルのシステム(64個のトランスミッタと64個のレシーバーを

ンスミッタは、ほとんどの時間、アクティブではなくなるので、

搭載)を設定する方法について説明します。ここでいうチャンネ

SLPが消費電力を抑える上で鍵を握ることになります。しかし、

ル・ベースのスキャンとは、1つの周波数ですべての送信チャン

SLPから送信モードへの切り替えに必要な時間(50ナノ秒)は、

ネルを掃引し、その後、周波数をインクリメントして同じ処理を

システムの観点からはあまりにも長いと言えます。この時間は、

繰り返すというものです。

掃引時の遅延につながるおそれがあります。RDYは、ICが送信

図6は、16個のADAR2001を対象として上記の掃引を実行する の準備を整えるときに指定できる中間状態だと言うこともできま

場合に、ステート・マシンをどのようにプログラムすればよいの す。図6の状態4において、IC 1のチャンネル4が送信を行って

かを示したものです。このアーキテクチャの主な目的は、共通の いる際、IC 2はRDYに遷移して送信の準備に入る点に注目して

制御ラインによって異なる処理を実行する複数のデバイスのシー ください。

ケンス制御を可能にすることです。

6 エッジ処理をベースとするミリ波対応のセキュリティ用スキャナを実現する

Page7

トランスミッタが状態4から状態5に遷移すると、IC 1は送信 ん)。3つの周波数は、必ず異なる値でなければなりませんが、掃

モードからRDYに遷移し、IC 2はRDYから送信モードに遷移し 引時には互いに近い周波数を使用する必要があります。例えば、

ます。この遷移にかかる時間は10ナノ秒です。それに続き、内 1つのADAR2001の1つのチャンネルが10GHzで送信を行う場

部で行われるチャンネルの切り替え(IC 2のチャンネル1から、 合、他の2つのデバイスによって10.025GHzと10.050GHzで

チャンネル2、チャンネル3、チャンネル4への切り替え)にか 送信を行うといった具合です。その結果、50MHz、75MHz、

かるスイッチング時間は2ナノ秒です。1024素子から成るアレ 100MHzのIF出力が得られます。このように実装するには、送

イにおいて、0.1GHzのステップで10GHz~40GHzの掃引を行 信側のパスに、より多くのハードウェアとスイッチング用のイン

う場合、トータルのスキャン時間は20ミリ秒未満になります。 フラが必要になります。その一方で、トータルのスキャン時間を

これは、PLLのロック時間が50マイクロ秒だと仮定した場合の値 1/3に短縮できるというメリットが得られます。

です。2個のPLLをピンポン・モードで動作させ、周波数が決ま

るまでのセトリング時間を短縮すれば、スキャン時間を5ミリ秒 まとめ

未満に抑えることが可能になります。 本稿では、ミリ波イメージングを利用して実現されるスキャナ

ADAR2004(レシーバー)の動作とシーケンス制御は、それほ の設計について解説しました。具体的な例としては、アナログ・

ど複雑ではありません。すべてのレシーバーのチャンネルは、常 デバイセズが提供するチップセットを採用した実装を紹介しまし

時受信動作をするように設定するのが一般的だからです。ただ、 た。その中で中核的な役割を果たすのは、クワッドトランスミッ

レシーバーがトランスミッタの動作に合わせて掃引を行う際に タのADAR2001、クワッドレシーバーのADAR2004、16チャ

は、マルチプレクサのパスとフィルタの設定が適切に選択される ンネルのADCであるAD9083、PLL/VCOのADF4368です。

ように、やはりステート・マシンのシーケンス制御が必要になり これらのICを採用すれば、ウォークスルー方式の次世代スキャナ

ます。 の実装に必要な高い集積度と高度な機能を利用できます。各IC

が備えるステート・マシンとDDCを活用することにより、従来

先述したとおり、AD9083(CTSD ADC)の各チャンネルでは、 は中央に集中していた処理の多くをインテリジェントなエッジに

最大3つの直交DDCチャンネルを利用できます。これは、3つ オフロードすることができます。その結果、中央のプロセッサは、

の周波数を同時に復調可能であるということを意味します。但 スキャンを行う際にシステムを制御する必要がなくなります。既

し、それは3つすべての周波数が同ADCのアナログ入力帯域幅 に復調とデシメーションを終えたデータを受信するだけでよいと

(125MHz)の範囲内にある場合に限られます。例えば、3つの いうことです。本稿で紹介したチップセットは、セキュリティの

IFトーンを50MHz、75MHz、100MHzに設定すれば、3つすべ 用途に向けたミリ波イメージングを対象として設計されたもので

てを同時にベースバンドのI/Qデータに復調することができます。 す。ただ、ADAR2001/ADAR2004が対応する広い周波数範囲

この方法を送信側に適用するには、1つではなく3つの送信側PLL と、16チャンネルのADCであるAD9083の高い集積度は他の

を使用しなければなりません。3つの送信周波数は、それぞれ物 アプリケーションにおいても有用です。つまり、それらのICは、

理的に異なる送信ICに振り分ける必要があります(ADAR2001 高いチャンネル密度と高速なスイッチングを必要とするシステム

の逓倍器は、マルチトーンの信号を通過させることができませ でも有効に活用できます。

著者について

Eamon Nashは、アナログ・デバイセズのアプリケーション・エンジニアリング・ディレクタです。衛星通

信やレーダーで使用されるRFアンプやビームフォーマを担当しています。30年間にわたり、フィールドや

工場で様々な業務に従事。主に、ミックスドシグナル製品や高精度製品、RF製品を扱ってきました。アイル

ランドのリムリック大学で電子工学の学士号を取得。5件の特許を保有しています。

VISI T A N A L O G . C O M /JP

お住いの地域の本社、販売代理店などの情報は、analog. ©2023 Analog Devices, Inc. All rights reserved.

com/jp/contact をご覧ください。 本紙記載の商標および登録商標は、各社の所有に属します。

Ahead of What’s Possibleはアナログ・デバイセズの商標です。

オンラインサポートコミュニティEngineerZoneでは、アナ

ログ・デバイセズのエキスパートへの質問、FAQの閲覧がで

きます。 AD5704-0-4/23

VISIT ANALOG.COM/JP 7