マシンビジョンコンポーネント:画像取り込み、解析および転送

www.euresys.com/s2i

GigE Vision IP コア

FPGA用GIGE VISION IPコア

概要

• Xilinx 7シリーズ (およびそれ以上) およびIntel (Altera Cyclone Vデバイス (およびそれ以上) 対応

• コンパクト、カスタマイズ可能

• 100Mb/sから10Gb/s以上のリンク速度サポート

• フル機能のリファレンスデザインとともに提供

GigE Visionは、普及しているイーサネット技術に基づいたビジョンアプリケーション用の標準的な通信プロトコルです。このプ

ロトコルを使用することで、TCP/IPプロトコルファミリーを使用している複数のPCとGigE Visionデバイスを簡単につなぐことが

できます。Sensor to Imageは、GigE Visionインターフェースを使用してFPGAベースの製品を構築するためのIPコアと開発フレ

ームワークのセットを提供します。GigE Visionの速度、特に1Gb/s以上の速度であるため、送信側と受信側では、エンベデッド

GigEコアをFPGAベースで高速に実装する必要があります。GigE VisionコアはXilinx 7シリーズ デバイス (およびそれ以上) およ

びIntel/Altera Cyclone Vデバイス (およびそれ以上) と互換性があります。

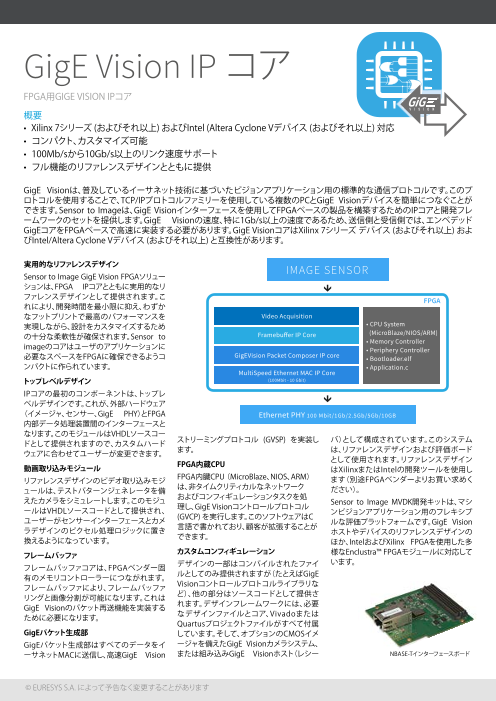

実用的なリファレンスデザイン

Sensor to Image GigE Vision FPGAソリュー

IMAGE SENSOR IMAGE SENSOR IMAGE SENSOR

ションは、FPGA IPコアとともに実用的なリ

ファレンスデザインとして提供されます。こ FPGA FPGA FPGA

れにより、開発時間を最小限に抑え、わずか

なフットプリントで最高のパフォーマンスを ���� �������� ���� ��������

��������������������� ���� ��������

実現しながら、設計をカスタマイズするため

� ���������

� ���������

の十分な柔軟性が確保されます。Sensor to

��������� ��� ������������� �

�������� ������� ������������ �

imageのコアはユーザのアプリケーションに

������� ���

���������� ������� �

���������������� ������� ������

�������� �������

必要なスペースをFPGAに確保できるようコ �������������� �������������

��������

�

���������� �������

ンパクトに作られています。

� ������

�

� ������

�

����������������� ��� ��� �������������������������

����� ������ �������������トップレベルデザイン �����������������

IPコアの最初のコンポーネントは、トップレ

ベルデザインです。これが、外部ハードウェア

(イメージャ、センサー、GigE PHY)とFPGA ���������������������������

������������ ������

� �� �������������������� �����

内部データ処理装置間のインターフェースと

なります。このモジュールはVHDLソースコー �������

ドとして提供されますので、カスタムハード ストリーミングプロトコル (GVSP) を実装し バ)として構成されています。このシステム

ウェアに合わせてユーザーが変更できます。 ます。 は、リファレンスデザインおよび評価ボード

FPGA内蔵CPU として使用されます。リファレンスデザイン動画取り込みモジュール はXilinxまたはIntelの開発ツールを使用し

リファレンスデザインのビデオ取り込みモジ FPGA内臓CPU( MicroBlaze、NIOS、ARM) ます(別途FPGAベンダーよりお買い求めく

ュールは、テストパターンジェネレータを備 は、非タイムクリティカルなネットワーク ださい)。

えたカメラをシミュレートします。このモジュ およびコンフィギュレーションタスクを処 Sensor to Image MVDK開発キットは、マシ

ールはVHDLソースコードとして提供され、 理し、GigE Visionコントロールプロトコル ンビジョンアプリケーション用のフレキシブ

ユーザーがセンサーインターフェースとカメ (GVCP) を実行します。このソフトウェアはC

ラデザインのピクセル処理ロジックに置き 言語で書かれており、顧客が拡張することが

ルな評価プラットフォームです。GigE Vision

換えるようになっています。 できます。

ホストやデバイスのリファレンスデザインの

ほか、IntelおよびXilinx FPGAを使用した多

フレームバッファ カスタムコンフィギュレーション 様なEnclustra™

FPGAモジュールに対応して

フレームバッファコアは、FPGAベンダー固 デザインの一部はコンパイルされたファイ

います。

有のメモリコントローラーにつながれます。 ルとしてのみ提供されますが(たとえばGigE

フレームバッファにより、フレームバッファ Visionコントロールプロトコルライブラリな

リングと画像分割が可能になります。これは ど)、他の部分はソースコードとして提供さ

GigE Visionのパケット再送機能を実装する れます。デザインフレームワークには、必要

ために必要になります。 なデザインファイルとコア、Vivadoまたは

Quartusプロジェクトファイルがすべて付属

GigEパケット生成部 しています。そして、オプションのCMOSイメ

GigEパケット生成部はすべてのデータをイ ージャを備えたGigE Visionカメラシステム、

ーサネットMACに送信し、高速GigE Vision または組み込みGigE Visionホスト(レシー NBASE-Tインターフェースボード

© EURESYS S.A. によって予告なく変更することがあります

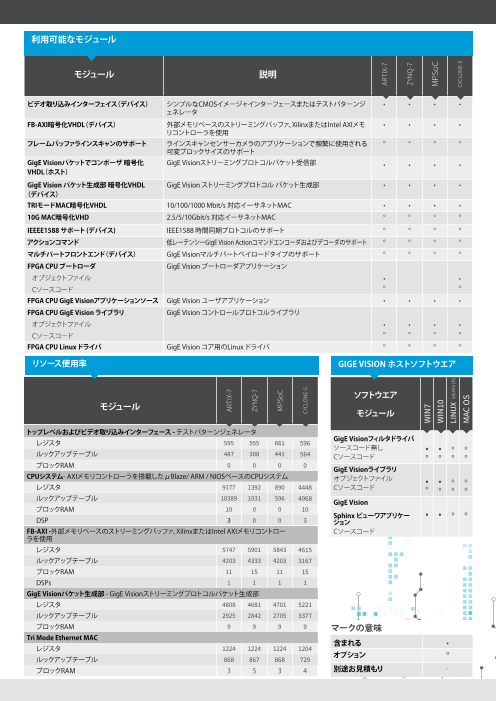

利用可能なモジュール

モジュール 説明

ビデオ取り込みインターフェイス(デバイス) シンプルなCMOSイメージャインターフェースまたはテストパターンジ • • • •

ェネレータ

FB-AXI暗号化VHDL(デバイス) 外部メモリベースのストリーミングバッファ、XilinxまたはIntel AXIメモ • • • •

リコントローラを使用

フレームバッファラインスキャンのサポート ラインスキャンセンサーカメラのアプリケーションで頻繁に使用される ᵒ ᵒ ᵒ ᵒ

可変ブロックサイズのサポート

GigE Visionパケットでコンポーザ 暗号化 GigE Visionストリーミングプロトコルパケット受信部 • • • •

VHDL(ホスト)

GigE Vision パケット生成部 暗号化VHDL GigE Vision ストリーミングプロトコル パケット生成部 • • • •

(デバイス)

TRIモードMAC暗号化VHDL 10/100/1000 Mbit/s 対応イーサネットMAC • • • •

10G MAC暗号化VHD 2.5/5/10Gbit/s 対応イーサネットMAC ᵒ ᵒ ᵒ ᵒ

IEEEE1588 サポート (デバイス) IEEE1588 時間同期プロトコルのサポート ᵒ ᵒ ᵒ ᵒ

アクションコマンド 低レーテンシーGigE Vision Actionコマンドエンコーダおよびデコーダのサポート ᵒ ᵒ ᵒ ᵒ

マルチパートフロントエンド(デバイス) GigE Visionマルチパートペイロードタイプのサポート ᵒ ᵒ ᵒ ᵒ

FPGA CPU ブートローダ GigE Vision ブートローダアプリケーション

オブジェクトファイル • •

Cソースコード ᵒ ᵒ

FPGA CPU GigE Visionアプリケーションソース GigE Vision ユーザアプリケーション • • • •

FPGA CPU GigE Vision ライブラリ GigE Vision コントロールプロトコルライブラリ

オブジェクトファイル • • • •

Cソースコード ᵒ ᵒ ᵒ ᵒ

FPGA CPU Linux ドライバ GigE Vision コア用のLinux ドライバ ᵒ ᵒ ᵒ ᵒ

リソース使用率 GIGE VISION ホストソフトウエア

ソフトウエア

モジュール

モジュール

トップレベルおよびビデオ取り込みインターフェース - テストパターンジェネレータ

レジスタ 595 555 661 596 GigE Visionフィルタドライバ

ソースコード無し

ルックアップテーブル

• •

487 308 441 564 ᵒ ᵒCソースコード ᵒ ᵒ ᵒ ᵒ

ブロックRAM 0 0 0 0 GigE Visionライブラリ

CPUシステム- AXIメモリコントローラを搭載したμBlaze/ ARM / NIOSベースのCPUシステム オブジェクトファイル • •

レジスタ 9177 1392 890 4448 Cソースコード ᵒ ᵒᵒ ᵒ ᵒ ᵒ

ルックアップテーブル 10389 1031 596 4068 GigE Vision

ブロックRAM 10 0 0 10

DSP

Sphinx ビューワアプリケー • •

3 0 0 3

ᵒ ᵒ

ション

FB-AXI -外部メモリベースのストリーミングバッファ、XilinxまたはIntel AXIメモリコントロー Cソースコード

ラを使用

レジスタ 5747 5901 5843 4615

ルックアップテーブル 4203 4333 4203 3167

ブロックRAM 11 15 11 15

DSPs 1 1 1 1

GigE Visionパケット生成部 - GigE Visionストリーミングプロトコルパケット生成部

レジスタ 4808 4681 4701 5221

ルックアップテーブル 2925 2842 2705 3377

ブロックRAM 9 9 9 9 マークの意味

Tri Mode Ethernet MAC

含まれる •

レジスタ 1224 1224 1224 1204

ルックアップテーブル オプション868 867 868 729 ᵒ

ブロックRAM 3 5 3 4 別途お見積もり -

ARTIX-7

ZYNQ-7

MPSoC

CYCLONE-5

ARTIX-7

ZYNQ-7

WIN7

WIN10

MPSoC

LINUX (UBUNTU LTS)

CYCLONE-5

MAC OS

USB3 Vision IP コア

FPGA用USB3 VISION IPコア

概要

• Xilinx 7シリーズ (およびそれ以上) およびIntel Cyclone Vデバイス (およびそれ以上) 対応

• コンパクト、カスタマイズ可能

• 実用的なリファレンスデザインが付属

USB3 Visionは、広く使用されているUSB 3.0インターフェースを使用したビジョンアプリケーション用の標準通信プロトコル

です。これは標準のプロトコルで、GenICamをサポートしているため、カメラとPCを簡単に接続することができます。Sensor to

Imageは、USB3 Visionインターフェースを使用してFPGAベースの製品を構築するためのIPコアと開発フレームワークのセット

を提供します。USB3 Visionの速度により、送信側と受信側では、エンベデッドUSBコアをFPGAベースで高速に実装する必要が

あります。USB3 VisionコアはXilinx 7シリーズ デバイス (およびそれ以上) およびIntel/Altera Cyclone Vデバイス (およびそれ以

上) と互換性があります。

実用的なリファレンスデザイン

Sensor to Image USB3 Vision FPGAソリュ

IMーAシGョEン はS、EFNPGSA OIRPコアとともに実用的な IMAGE SENSOR IMAGE SENSOR

リファレンスデザインとして提供されます。こ

れにより、開発時間を最小限に抑え、わずか

なフットプリントで最高のパフォーマンスFPをGA FPGA FPGA

���� ���実���現��しながら、設計をカスタマイズするため ���� ��������

の十分な柔軟性が確保

� さ��れ��ま��す��。�Sensor to ���������������������

���� ��������

�������i�m� a�g��eのコアはユーザ��の��ア���プ��リケ��ーショ�� ン�に

� ���������

必要なスペースをFPG

�A�に��確��保�� で��き��る�よ��うコ ������������ �

������� ���

ンパクトに作られていま

��す���。����� ������� �

����������������

������� ������

�������� �������

�������������� �������������

��������

�

���������� �������

トップレベルデザイン

� ������

�

� ������

�

����������������� ��� ��� �������������������������

IPコアの最初のコンポーネントは、トップレ ����� ������ ������������������������������

ベルデザインです。これが、外部ハードウェア

(イメージャ、センサー、USB3 PHY)とFPGA

�����������

内

�

部

�

データ処理装置間のインターフェース

とな

�

り

��

ま

��

す

���

。

�

こ

��

の

��

モ

�

�

ジ

��

ュ

��

ー

��

ル

��

を

��

V

�

HDLソースコ

������

� �� �������������������� �����

ードとして提供し、カスタムハードウェアに �������

適合させることができます。

動画取り込みモジュール

リファレンスデザインのビデオ取り込みモジ Cypress FX3 使用します(別途FPGAベンダーよりお買い

ュールは、テストパターンジェネレータを備 Cypress FX3チップ(内臓ARM CPUおよび 求めください)。

えたカメラをシミュレートします。このモジュ 物理インターフェースを含む)は、あらゆる Sensor to Image MVDK開発キットは、マシ

ールはVHDLソースコードとして提供され、 USB3初期化ルーチンおよびUSB3 Vision制 ンビジョンアプリケーション用のフレキシブ

ユーザーがセンサーインターフェースとカメ 御チャンネル通信を処理するために使用し ルな評価プラットフォームです。USB3 Vision

ラデザインのピクセル処理ロジックに簡単 ます。 デバイスデザインのほか、IntelおよびXilinx

に置き換えられるようになっています。 カスタムコンフィギュレーション FPGAを使用した多様なEnclustra™ FPGAモ

USB3 Visionストリーミングプロトコル パケッ ジュールに対応しています。 デザインの一部はコンパイルされたファ

ト生成部 イル(たとえばUSB3 Visionコントロールプ

USB3 Visionストリーミングプロトコル パケ ロトコルライブラリなど)で、他の部分はソ

ット生成部は、ビデオソースからすべてのデ ースコードとなります。デザインフレーム

ータを取得し、USB3 Visionストリーミングパ ワークには、必要なデザインファイルとコ

ケットを構築します。また、USB3 PHYへの低 ア、VivadoまたはQuartusプロジェクトファ

レベルの通信もすべて処理します。 イルがすべて付属しています。オプションの

フレームバッファコア CMOSイメージャを備えたUSB3 Visionカメ

ラシステムとして構成されています。このシ

フレームバッファコアは、FPGAベンダー固 ステムは、リファレンスデザインおよび評価

有のメモリコントローラーにつながれます。 ボードとして使用されます。リファレンスデ

フレームバッファは、カメラとPC間の通信遅 ザインはXilinxまたはIntelの開発ツールを

延を調整するために使用されます。 USB3 インターフェイスボード

© EURESYS S.A. によって予告なく変更することがあります

利用可能なモジュール

モジュール 説明

ビデオ取り込み シンプルなCMOSイメージャイ • • •

インターフェイス ンターフェースまたはテストパターンジェネレータ

FB-FIFO BlockRAMベースのストリーミン

暗号化VHDL グバッファ • • •

VHDL ソースコード ᵒ ᵒ ᵒ

FB-AXI 暗号化 VHDL 外部メモリベースのストリーミ ᵒ ᵒ ᵒ

ングバッファ、XilinxまたはIntel

AXIメモリコントローラを使用

USB3 Vision パケット生成部 USB3 Visionストリーミングプロ

暗号化VHDL トコル パケット生成部

VHDL ソースコード • • •

ᵒ ᵒ ᵒ

FX3 USB3 Vision アプリケー USB3 Vision ユーザアプリケー • • •

ションソースコード ション

FX3 USB3 Vision ライブラリ USB3 Vision コントロールプロ

オブジェクトファイル トコルライブラリ • • •

Cソースコード ᵒ ᵒ ᵒ

リソース使用率 USB3 VISION ホストソフトウエア

ソフトウエア

モジュール モジュール

トップレベルおよびビデオ取り込みインターフェース - テストパターンジェネレータ USB3 Visionドライバ

レジスタ 622 623 679 ソースコード無し • • ᵒ -

ルックアップテーブル 381 424 551 Cソースコード ᵒ ᵒ ᵒ -

ブロックRAM 0 0 0 USB3 Visionライブラリ

CPUシステム - - AXIメモリコントローラを搭載したµBlaze/ARM/NIOSベースのCPUシステム オブジェクトファイル • •

Cソースコード ᵒ

-

レジスタ 7642 1897 3523 ᵒ ᵒ ᵒ -

ルックアップテーブル 8864 1564 3341 USB3 Vision

Sphinx ビューワアプリケー

ブロックRAM 6 1 49 ション • • ᵒ -

DSP 3 0 3 Cソースコード

FB-FIFO - BlockRAMベースのストリーミングバッファ (64kB)

レジスタ 1892 1890 2038

ルックアップテーブル 811 808 1077

ブロックRAM 16 16 64

DSP 5 5 4

FB-AXI -外部メモリベースのストリーミングバッファ、XilinxまたはIntel AXIメモリコントローラを使用

レジスタ 4360 4326 4615

ルックアップテーブル 3296 3284 3167

ブロックRAM 6 6 15 マークの意味

USB3 Visionパケット生成部 - USB3 Visionストリーミングプロトコルパケット生成部 含まれる •

レジスタ 2743 2727 2936

オプション ᵒ

ルックアップテーブル 2127 2117 2386

ブロックRAM 1 1 4 別途お見積もり -

ARTIX-7 ARTIX-7

ZYNQ-7 ZYNQ-7

CYCLONE-5 CYCLONE-5

WIN7

WIN10

LINUX (UBUNTU LTS)

MAC OS

CoaXPress IPコア

FPGA用COAXPRESS IPコア

概要

• Xilinx 7シリーズ (およびそれ以上) およびIntel

Cyclone Vデバイス (およびそれ以上) 対応

• コンパクト、カスタマイズ可能

• 1Gb/sから50Gb/sを超える速度サポート

• 実用的なリファレンスデザインが付属

CoaXPressは、広く使用されている同軸ケーブルを使用したビジョンアプリケーション用の標準通信プロトコルです。このプロ

トコルはカメラとフレームグラバーの接続を容易にするもので、標準のGenICamソフトウェアをサポートしています。Sensor

to Image CoaXPressインターフェースはFPGAベースの製品を構築するための一連のIPコアと開発フレームワークを提供しま

す。CXPの速度により、送信側および受信側ではCXPコアをFPGAベースで高速に実装する必要があり、できればエンベデッドト

ランシーバを使用することが推奨されます。CXPコアはXilinx 7シリーズ デバイス (およびそれ以上) およびIntel/Altera Cyclone

Vデバイス (およびそれ以上) と互換性があります。

実用的なリファレンスデザイン

IMAGE SENSOR SensoIMr toA GImEag eS CEXNP SFPOGARソリューション IMAGE SENSOR

は、FPGA IPコアとともに実用的なリファレン

スデザインとして提供されます。これにより、

FPGA 開発時間を最小限に抑え、わずかなフットプ FPGA FPGA

���� �������� リントで最高��の��パ �フォ����ー���マンスを実現しな

� ��������� がら、設�計�を�������������������

���� ��������

カスタマイズするための十分な

��������� ��� ������������� � 柔軟性が確保されます。Sensor to imageの

� ���������

�������� ������� コアはユーザのアプ ������������ �

������リ� ケ���ーションに必要な

���������� ������� �

���������������� ������� ������

�������� �������

�������������� ������������� スペースをFPGAに確保できるようコンパク

��������

�

���������� �������

� ������

� トに作られています。

� ������

�

����������������� ��� ��� �������������������������

����������������� トップレベル�デ�ザ���イ �ン� ���� �������������

IPコアの最初のコンポーネントは、トップレ

ベルデザインです。これが、外部ハードウェア

������������� (イメージャ、センサー、CXP PHY)とFPGA��������������

������������ ������

� �� �������������������� �����

内部データ処理装置間のインターフェース

となります。こ�の��モジ��ュ��ールはVHDLソースコ

ードとして提供されますので、カスタムハー

ドウェアに合わせてユーザーが変更できま FPGA内蔵CPU ツールを使用します(別途FPGAベンダーよ

す。 FPGA内蔵CPU (MicroBlaze、NIOS、ARM) りお買い求めください)。

動画取り込みモジュール

は、CXPレシーバまたはトランスミッタコア Sensor to Image MVDK開発キットは、マシ

での非タイムクリティカルな制御およびコン ンビジョンアプリケーション用のフレキシブ

リファレンスデザインのビデオ取り込みモジ フィギュレーションタスクに使用されます。こ ルな評価プラットフォームです。CoaXPress

ュールは、テストパターンジェネレータを備 のソフトウェアはC言語で書かれており、顧 ホストやデバイスのリファレンスデザインの

えたカメラをシミュレートします。このモジュ 客が拡張することができます。 ほか、IntelおよびXilinx FPGAを使用した多

ールはVHDLソースコードとして提供され、

ユーザーがセンサーインターフェースとカメ カスタムコンフィギュレーション

様なEnclustra™ FPGAモジュールに対応して

います。

ラデザインのピクセル処理ロジックに置き デザインの一部はコンパイルされたファイル

換えるようになっています。 (たとえばCXPコントロールプロトコルライ

CoaXPressストリーミングインターフェイス ブラリなど)で、他の部分はソースコードと

CXPストリーミングインターフェイスは、ビデ

なります。デザインフレームワークには、必

オセンサーからCXP PHYに出力される全デ

要なデザインファイルとコア、Vivadoまたは

ータを受信します。CXP仕様に応じて、ストリ

Quartusプロジェクトファイルがすべて付属

ーミングチャンネルで最高速度に達します。

しています。オプションのCMOSイメージャ

を備えたCXPカメラシステム、または組み込

CoaXPress制御インターフェイス みCXPホスト(レシーバ)として構成されてい

CXP制御インターフェイスは、CXP制御チャ ます。このシステムは、リファレンスデザイン

ンネルおよびCXP PHYから/へ送られる全デ および評価ボードとして使用されます。リフ

ータを送受信し、CXP仕様に従って制御チャ ァレンスデザインはXilinxまたはIntelの開発

CXPインターフェースボード

ネルを実装します。

© EURESYS S.A. によって予告なく変更することがあります

利用可能なモジュール

モジュール 説明

ビデオ取り込みインターフェイス シンプルなCMOSイメージャイ

(デバイス) ンターフェースまたはテストパ • • • •

ターンジェネレータ

CXP パケットデコンポーザ CoaXPressストリーミングプロト

(ホストコア) コルパケット受信部

暗号化VHDL • • • •

VHDL ソースコード

ᵒ ᵒ ᵒ ᵒ

CXP パケット生成部 CoaXPressストリーミングプロト

(デバイスコア) コルパケット生成部

暗号化VHDL • • • •

VHDL ソースコード ᵒ ᵒ ᵒ ᵒ

CXP12速度サポート 64ビットピクセルインターフェ

イスによるCXP12のサポート ᵒ ᵒ ᵒ ᵒ

FPGA CPU CoaXPress CoaXPressユーザーアプリケー

アプリケーションソースコード ション • • • •

FPGA CPU CoaXPress CoaXPressコントロールプロト

ライブラリ コルライブラリ • • • •

オブジェクトファイル ᵒ ᵒ ᵒ ᵒ

Cソースコード

リソース使用率

モジュール

トップレベルおよびビデオ取り込みインターフェース - テストパターンジェネレータ

レジスタ 473 445 445 575

ルックアップテーブル 338 290 288 579

ブロックRAM 0 0 0 1

CPUシステム-μBlaze/ARM/NIOSベースのCPUシステム

レジスタ 987 3051 835 3621

ルックアップテーブル 708 3236 558 3663

ブロックRAM 0 16 0 42

DSP 0 3 0 3

CXP パケット生成部 (デバイスコア)

レジスタ 9794 9701 11640 11152

ルックアップテーブル 7829 7606 9109 11461

ブロックRAM 15 15 15 60

DSPs 4 4 4 4

GigE Visionパケット生成部 - GigE Visionストリーミングプロトコルパケット生成部 マークの意味

レジスタ 6394 6280 8722 8722 含まれる •

ルックアップテーブル 5297 5159 7171 7171

オプション ᵒ

ブロックRAM 18 18 18 18

送信部 4 4 4 4 別途お見積もり -

ZYNQ7 ZYNQ7

KINTEX KINTEX

ULTRASCALE ULTRASCALE

MPSoC MPSOC

CYCLONE

-10

CYCLONE -10

IMX Pregius IP Core

SONY IMX PREGIUS SUB-LVDSイメージセンサー用のIPコア

概要

• センサー画像出力のSub-LVDS読み出しとその復号ブロック

• SPIベースのセンサー操作設定モジュール

• センサー操作設定ソフトウェアライブラリ

• フリーランニングまたはトリガ読み出しモード対応

Sony製のIMX Pregiusは、広く使用されている高品質CMOSイメージセンサーのシリーズです。Sensor to Image IMX Pregius IP

コアは画像データを効率的に読み取り、センサーの動作を制御します。Sensor to ImageMVDKおよび標準FPGA評価キットと

互換性のあるFMCモジュールとともに、リファレンスデザインとして提供されています。これを使うことにより、カメラを簡単に設

計することが可能です。

SubLVDSレシーバとデシリアライザ

Sub-LVDSレシーバとデシリアライザブロッ

クはセンサーの出力ピンと接続し、FPGA IO IMX Pregius IP Core

セルを使用してイメージストリームをパラレ

ルデータ化します。このブロックはFPGAに依 Clock

存しており、現在、Xilinx FPGAに使用できま Input �������

Frame valid

す。パラレルビデオストリームはクロッピン Stream ������������ ������� Line valid

グすることができ、さらなる処理のためにカ ���������

�� Data

メラリンクのようなフォーマットで供給され

ます。

トリガジェネレータ XHS

IMX Pregiusセンサーは、フリーランニング XVS �����

� ��������

モードまたはスレーブモードがあり、どちら XTRIG

もコアのタイミングおよびトリガジェネレー

タを使用して駆動できます。SPIベースのセ SCLK

ンサ制御インタフェースは、要求タイミング

に対応しセンサの操作を可能にしています。

制御レジスタ Control ��������������

�������

Interface ��������� ��

������

IPコアの機能は、コンパイル時のパラメー

タ、または実行時にAXI-Liteインタフェース

を使用する制御レジスタによってコントロー

ルします。Cソフトウェアライブラリは、センサ AXI 4-Lite

とIPコアをコントロールします。

付属品

IPコアには、センサーと標準FPGA評価ボー

ド間のインタフェースとなるFMC(FPGAメ

ザニンカード)を含む完全なリファレンス

デザインが付属しています。FMCモジュー

ルはFMC-LPCに準拠しており、IMX Pregius

CMOSセンサーが必要とするすべての電力

と電位の調整を行います。

IMXインタIMーフX ェPrーegスiuボsインターフェイス

ボーードドを装備したMVDK

© EURESYS S.A. によって予告なく変更することがあります

利用可能なモジュール

モジュール 説明

IMX IPコア Sub-LVDS IMX Pregius IP

暗号化VHDL • • •

VHDL ソースコード ᵒ ᵒ ᵒ

IMX IP ソフトウエアライブラリ コアとイメージャを制御するCソースコ

オブジェクトファイル ードAPI • • •

Cソースコード ᵒ ᵒ ᵒ

GigE Visionインターフェー

スを備えたレファレンスデ • • •

ザイン

リソース使用率 センサーの対応状況

モジュール センサーボー

第三者の シミュ レー

モジュール ハード ウェア ションで

ドの対応状況

で動作済み 検証済み

IMX IPコア12ビット4チャンネル構成 IMX174 ✓ ✓ ✓

レジスタ 1544 1544 1544

ルックアップテーブル

IMX249

1722 1722 1722 ✓ ✓

ブロックRAM 1 1 1 IMX302 ✓

IMX IPコア12bit 8チェンネル IMX252 ✓ ✓ ✓

レジスタ 2064 2064 2064 IMX265 ✓ ✓

ルックアップテーブル 2352 2352 2352 IMX250 ✓ ✓ ✓

ブロックRAM 1 1 1 IMX264 ✓ ✓

IMX IPコア12bit 16チェンネル IMX255 ✓ ✓ ✓

レジスタ 3104 3104 3104 IMX267 ✓ ✓

ルックアップテーブル 3599 3599 3599

IMX305

ブロックRAM 1 1 1 ✓

IMX253 ✓ ✓ ✓

マークの意味

IMX304 ✓

含まれる • IMX273 ✓ ✓ ✓

オプション ᵒ IMX287 ✓

別途お見積もり -

ARTIX7

KINTEX7

ZYNQ7

ARTIX7

KINTEX7

ZYNQ7

MIPI CSI-2レシー

バIPコア

MIPI CSI-2イメージャ用IPコア

概要

• MIPI CSI2レシーバと復号ブロック

• 構成可能なMIPIレーン数

• Xilinx D-PHY IPを使用

• 迅速な開発のためのリファレンスデザインが付属

マシンビジョン業界では、MIPI CSI2インターフェースを使用するイメージャの普及が広まっています。そのうち多くの分野では、

高度な画像の前処理やホストシステムへの転送増加のために、FPGAとの接続が必要とされています。Sensor to ImageのMIPI

CSI-2レシーバIPコアは、FPGAのMIPIセンサーから送られるビデオストリームをデコードするためのソリューションを提供しま

す。それにはMIPI D-PHY物理インターフェイスを実装するコンパニオンIPコアが必要になります。D-PHYレシーバは、PHYプロ

トコルインターフェイス(PPI)を使用してCSI-2レシーバに接続されます。MIPI CSI-2レシーバIPコアには、Sensor to Imageの

MVDKおよびIMX274 MIPI FMCモジュールを含む実用的なワーキングリファレンスデザインが付属しており、開発時間の短縮

に役立ちます。

主な機能 MIPI CSI-2 Receiver IP Core

• FPGA技術に依存しない

������

• さまざまなD-PHY実装に接続するための ��������� AXI 4-Lite

PPIインターフェイス

• 1、2、または4つのデータレーンに構成可能 Control/Status

• 任意のレーンレートに対応

• RAW8、RAW10、RAW12、RAW14、RAW16 ���� ������ ����� �����

PPI ���������� ������ ��������

���� CSI Video

標準MIPIデータ型に対応 �

�������

• 埋め込まれたデータのデコードが可能

• ピクセルのアンパックなしで、リオーダーさ

れたバイトストリームの直接出力が可能

• AXI4-Liteスレーブ制御インターフェイス 付属品

このコアには、Zynq Ultrascale +

コアは主に5つの部分から構成されていま FPGA、IMX274 MIPI FMCモジュール、GigE

す。パケットエンジンが組み合わされたレー Vision出力を備えたS2IのMVDK用の完全な

ン管理でパラレルバイトレーンが受信され リファレンスデザインが付属しています。物

ると、制御情報が抽出され、レーンのアライ 理インターフェイスはXilinx D-PHYコアによ

メントとバイトのリオーダーの実装が行わ って抽象化されているため、たとえば7シリ

れた後、最後にアライメントされたペイロー ーズXilinx FPGAなどの他のFPGAプラットフ

ドバイトストリームが提供されます。ピクセ ォームにもデザインを簡単に移植できます。

ルアンパッカーにより、これらのバイトストリ 利用可能なモジュール

ームからピクセルデータ型が抽出されます。 MIPI CSI2レシーバIPコアは、暗号化された

ピクセルストリームは出力ピクセルクロック VHDLとして提供されます。また、オプション

調整によって出力クロックドメインに変換 としてVHDLソースコードとして入手すること

されます。制御インターフェイスには、AXI4- もできます。Xilinx Artix7、Kintex7、Zynq7お

Liteスレーブインターフェイスを使用して よびUltrascale + FPGAと互換性があります。

CPUからアクセスできるコントロール/ステ

ータスレジスタのセットが含まれています。

MIPI CSI2レシーバIPソフトウェアライブラリ

は、オブジェクトファイルとして提供されま

す。また、オプションとしてCソースコードとし

て入手することもできます。 MIPI CSI-2 レシーバインターフェイス

ボードを装備したMVDK

© EURESYS S.A. によって予告なく変更することがあります

リソース使用率

モジュール

Xilinx MIPI D-PHY 4レーン

外部信号レベルの変換が必要(例:Meticomチップセット) はい なし

レジスタ 840 1188

ルックアップテーブル 2157 2261

ブロックRAM 0 0

4レーン、8ビットピクセル用に構成されたMIPI CSI-2レシーバIPコア

レジスタ 793 793

ルックアップテーブル 286 285

ブロックRAM 1 1

ARTIX7

KINTEX7

ZYNQ7

ZYNQ

ULTRASCALE+

MVDK

マシンビジョン開発キット

概要

• 1枚の開発ボードで主要なマシンビジョンインター

フェイスすべてに対応

• GigE Vision、CoaXPress、USB3 Visionに

準拠したプラットフォーム

• Sony IMX Pregius評価プラットフォーム

• GigE Visionは最大で10 GB/秒。

CoaXPressはCXP-12次第

• XilinxとIntel FPGAを使用した

Enclustra Mercury FPGAモジュールのサポート

Sensor to Image MVDK(マシンビジョン開発キット)は、S2IのIPコアをベースとし、主要な産業用ビジョンインターフェースを使

用した製品の評価と開発を容易にするハードウェアプラットフォームです。MVDKベースボードは、FMC(FPGAメザニンカード)

を使用することで高度に構成可能です。これはビジョンセンサーとのインターフェイスとなり、GigE Vision、USB3 Vision、および

CoaXPressカメラ(デバイス)の開発や、GigE VisionおよびCoaXPressホストのデザインを可能にします。

MVDKには、Enclustra Mercury FPGAモジュ GigE Vision開発用

ールとFMCインターフェイスボードが付属し GigE Vision開発用に提供されるMVDKは、

ています。また、選択した転送レイヤーイン 速度が10 Gbit/秒までのAIA GigE Vision仕

ターフェイスのリファレンスデザインも追加 様に準拠したカメラおよびホストアプリケ

されます。これらの製品をまとめて使用する ーションのデザインをサポートします。2.5、5

ことで、開発時間を最小限に抑え、わずかな 、10 Gbit/秒の速度の用途には、Sensor to

フットプリントで最高のパフォーマンスを実 Image NBase-T FMCモジュールが必要で

現しながら、設計をカスタマイズするための す。

十分な柔軟性が確保されます。

IMX Pregius開発用

CoaXPress開発用 Sensor to Image MVDKは、広く使用されて

CoaXPress開発用に提供されるMVDKには、 いる高品質イメージャCMOSシリーズ、Sony

デバイス(カメラ)またはホスト(フレームグ のIMX Pregiusセンサーシリーズに準拠して

ラバー)設計用の2つまたは4つのCXP-6ま います。Sensor to Imageでは専用のIPを使

たはCXP-12リンクを備えたFMCが含まれて 用してこれらのセンサーをサポートしてお

います。デバイスおよびホストのリファレン り、センサーからデータを読み出したりセン

スデザインは完全にCoaXPressに準拠して サーを制御することができます。リファレン

おり、JIIAの認定を受けています。 スデザインは、IMX IPコアとGigE Visionに準

拠した出力で構成されています。

USB3 Vision開発用

USB3 Vision開発に使用できるMVDKは、標 MIPI CSI-2開発用

準USB3コンポーネントの5 Gbit/秒技術がベ MIPI CSI-2レレシーバIPコアに付属のMVDK

ースになっており、現在最も費用対効果の高 は、MIPI CSI-2標準に準拠した、広く使用

い高速カメラの設計に使用できます。USB3 されている高品質イメージャを装備した

Vision IPコア開発キットはGenicamに完全 カメラの設計をサポートします。Sensor to

に準拠しており、AIAの認定を受けています。 Imageはセンサーからのデータ読み出しや

そのため、新しいUSB3 Visionカメラを設計 センサー制御をサポートしています。リファ

するための早道となります。USB3 Visionイ レンスデザインは、MIPI CSI-2レシーバIPコ

ンターフェースは、Cypress FX3 USB3チップ アとGigE Visionに準拠した出力で構成され

を採用しているSensor to Imageが設計した ています。

FMCを使用して実装されます。

© EURESYS S.A. によって予告なく変更することがあります

複数のENCLUSTRA MERCURYモデルをご用意しております:

MVDK SA1

ENCLUSTRA MERCURY SA1モジュールを搭載したMVDKボード

Altera Cyclone V ARMプロセッサベースのSoC FPGA

DDR3L SDRAM 1 GB

Quad SPI フラッシュ 64 MB

10/100/1000 イーサネットPHY

3.125 GB/秒 トランシーバ 5個

MVDK ZX5

ENCLUSTRA MERCURY ZX5モジュールを搭載したMVDKボード

Xilinx Zynq-7000シリーズ SoC FPGA 7015

DDR3 SDRAM 1 GB

NAND フラッシュ 512 MB

Quad SPI フラッシュ 64 MB

10/100/1000 イーサネットPHY

6.25 GB/秒 トランシーバ 4個

MVDK XU1

ENCLUSTRA MERCURY+ XU1モジュールを搭載したMVDKボード

Xilinx Zynq Ultrascale+ MPSoC XCZU6

DDR4 ECC SDRAM 2 GB

Quad SPI フラッシュ 64 MB

eMMC フラッシュ 16 GB

10/100/1000 イーサネットPHY

8+3 16 GB/秒 トランシーバ(両方のFMCコネクタを使用)

*注記:他の構成についてはお問い合わせください

昨日、今日、そして明日...

1996

P C I バス の 技 術 が P C の 世 界 に 普 及し始

1989 め、PCでの画像処理の可能性が広がりました。多くのPCがデータ転送速度を十分持つ

1989年に会社を設立しました。最初の製 ようになり、PC上でますます画像処理が行

品はPCの有無に左右されずにカメラの われるようになりました。1996年から現在ま 2017

信号を評価し、ライブビデオとして表示す で、Sensor to ImageはRamsesシリーズに必

ることが可能なSnofruとGisehという画像 要なフレームグラバーを提供してきました。

2017年11月24日、Euresys S.A.がSensor

to Imageを買収。既存のチームが持つ共

処理のボードでした。 同の知識を活用して 使用範囲とサービ

スをさらに拡大するため、 より大規模な

グループを確立しました。

1999年から

1992

現在まで

GigE Vision IPコアのAIA認定を受けて以

降、2008年にはUSB3 Vision IPコアはAIA認

1992年にCheops Bildverarbeitungs 定、CoaXPress IPコアはJIIA認定、GenICam

GmbHという会社を設立しました。当時 コンポーネントはEMVA認定を受け、市場

は、産業用のモジュラー式PC画像処理カ に導入されました。 XilinxとIntelは当社が

ードの開発を推進することを目指していま 選定したFPGAプラットフォームのパートナ

した。 ーですが、IPコアがあらゆるハードウェアプ

その他に、フレームグラバーボードPic- ラットフォームと互換性を持つように十分

tureBoyとKairoが開発されました。オンボ

に配慮しています。

ードの画像処理やカラーカメラのデジタ 2015年には、産業界のイメージングセンサ

ル化など、当時としては優れた可能性を ーに接続する最初のセンサーIPコアを市

提供していました。 場に投入しました。現在では、MIPIとFPGA

をつなげ、GigE Visionを10 Gbit/sをはる

かに超えるスピードに対応させるととも

に、CoaXPress標準を光ファイバーメディア

に開放する取り組みをしています。

当社の製品および設計サービスは、自動

車、工業、医療、セキュリティ、軍事、宇宙な

どさまざまな分野で世界中で広く使用され

ています。

代理店

Sensor to Image GmbH • Lechtorstrasse 20 • 86956 Schongau • Germany • www.euresys.com/s2i

S2I_Catalog_Oct19_Ja